2. 清华大学 工程物理系 北京 100084;

3. 同方威视技术股份有限公司 北京 100083

2. Department of Engineering Physics, Tsinghua University, Beijing 100084, China;

3. Nuctech Company Limited, Beijing 100083, China

核电子学是不同于通讯、工业自动化和消费等普通电子学的一个特殊领域。核电子学主要面向的前端是探测器和前置放大器,主要处理的信号大多数是普通领域不会涉及的信号,比如极弱小的电流信号(fA量级)、极快的光电倍增管输出脉冲信号(ns量级)等。核电子学的通道数会随着探测器的规模快速增加,成百上千甚至上万通道的数据采集系统十分常见。例如,目前在建的中国锦屏地下实验室二期(China Jinping Underground Laboratory-Ⅱ, CJPL-Ⅱ)工程,将实现中国暗物质实验(China Dark matter EXperiment, CDEX-1T)的实验目标[1],即采用吨量级高纯锗探测器阵列对暗物质进行直接探测,每个探测器(约1kg质量,共约1000个探测器单元)输出有4个慢信号和一个快信号。大型强子对撞机夸克实验(Large Hadron Collider beauty, LHCb),拥有4500t的探测器、上万通道的前端电子学和两级触发系统,其前端电子学的数据带宽高达40 TB·s-1 [2]。因此,数据读出作为核电子学领域的一个基本环节,对读出性能和带宽有较高的要求。

数据读出的接口有很多,比如常见的USB (Universal Serial Bus)接口、RS232接口、光纤接口、以太网接口等。近年来以太网接口越来越受到核电子学领域科研工作者的青睐,特别是在大型分布式网络中。主要的原因在于以太网接口对于各种PC (Personal Computer)端的操作系统,有成熟的接口驱动和编程,并且有商用的交换机网络和非屏蔽双绞线以及光纤等多种物理链路,能较好地满足分布式网络数据获取系统的需求。在传统数据读出模块的基础上,基于Xilinx公司的新型架构的Zynq-7000 All Programmable SoC,我们研制了新型读出模块ZYNQBee。

1 ZYNQBee硬件设计 1.1 ZYNQ与传统FPGA+处理器的对比ZYNQ系列是近几年Xilinx推出的集成7系列现场可编程阵列(Field-Programmable Gate Array, FPGA)和双核处理器的混合架构的芯片,其内部实现了高性能、高带宽的PS (Processor System)与PL (Programmable Logic)的互联,包括两路32位AXI (Advanced eXtensible Interface)从设备接口,两路32位AXI主设备接口(称为通用用途接口,General Purpose Ports),4路64位可配置带1KB缓存的高速AXI从设备接口(称为高性能用途接口,High Performance Purpose Ports),以及1路64位AXI ACP接口(称为加速器一致性接口,Accelerator Coherency Port)等[3]。此外,ZYNQ具有丰富的外围接口,例如双千兆网络接口、USB、SD存储卡等,可以运行嵌入式Linux以及uCOS等RTOS,并且Xilinx提供了一体化的开发应用环境Vivado以及wiki网络开放资源来支持开源开发。

最小封装和逻辑容量的ZYNQ系列芯片为XC7Z010 CLG-225,其FPGA部分采用Artix-7架构的7系列FPGA,内部包含了至少约28K的可配置逻辑模块(Configurable Logic Block, CLB),其处理器部分为双核的ARM Cortex-A9 32位处理器,最少可以运行在667MHz,最高可以达到1GHz。作为对比,目前常使用Xilinx公司的Spartan-6系列中的XC6SLX25这款FPGA,其内部资源有24 K逻辑单元。常用的比如Freescale公司的MPC5200B,是单核的PowerPC 32位处理器,它运行在400MHz。而最小的ZYNQ处理器是CLG225封装,芯片的大小是13mm×13mm,相比其他芯片要小很多。表 1比较了上述三种芯片的性能和尺寸。

| 表 1 ZYNQ与传统FPGA及处理器芯片的比较 Table 1 Comparison of ZYNQ with traditional FPGA and the processor |

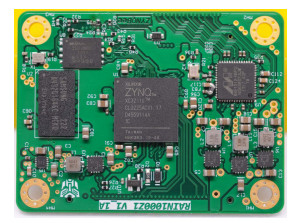

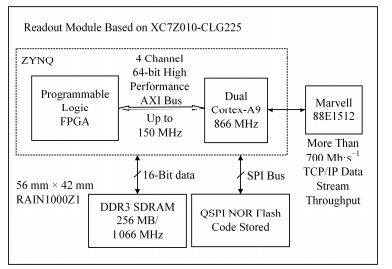

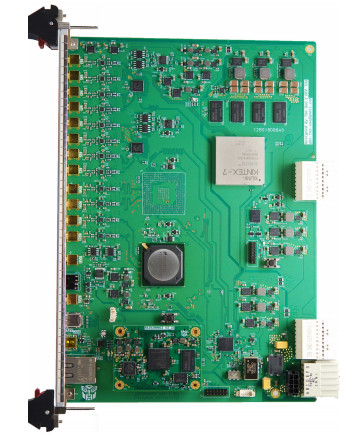

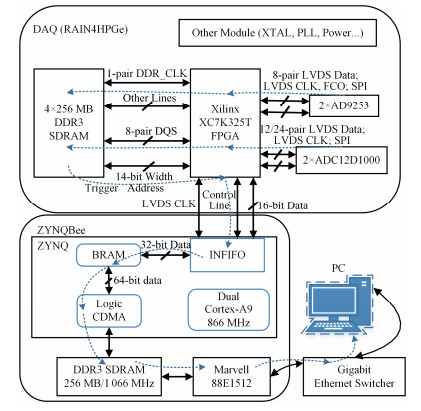

ZYNQBee是基于ZYNQ的具有千兆以太网接口的读出模块,其包含了XC7Z010-CLG225的ZYNQ芯片、16位数据总线宽度、256M容量的DDR3 (Double Data Rate 3) SDRAM (Synchronous Dynamic Random Access Memory)、千兆以太网的PHY以及QSPI接口的NOR Flash芯片。图 1是ZYNQBee读出模块的实物照片,整个ZYNQBee模块的大小是56mm×42mm,约是名片大小的一半。图 2是ZYNQBee读出模块的结构框图。

|

图 1 ZYNQBee读出模块的实物照片 Figure 1 Picture of ZYNQBee readout module |

|

图 2 ZYNQBee读出模块的结构框图 Figure 2 Block diagram of ZYNQBee readout module |

目前的ZYNQBee模块是基于ZYNQ系列的XC7Z010-CLG225芯片设计的,主要目的是在较小的尺寸下设计出高性能(具有千兆以太网接口)的读出模块。

在电源设计方面,XC7Z010需要1.0V作为内核电压,同时需要1.8V作为输入/输出(Input/Output)驱动和模拟部分的电源。如果使用DDR3 SDRAM,还需要1.5V的DDR3 SDRAM电源。每路电源电流的大小可以在Xilinx公司的Vivado开发软件中估算。

在实际模块设计中,使用了TI公司的TPS62130RGT[4]作为电压调节器,它可以在3~17V的输入范围内提供ZYNQBee模块需要的3.3V、1.8V、1.5V及1.0V电源,并且输出电流高达3A,另外TPS62130RGT本身尺寸只有3mm×3mm,配合Vishay公司的高性能超小尺寸的IHLP1212系列功率电感,可以在很小的尺寸内提供3A的电流。此外,使用了TI公司的TPS51206[5]来产生DDR3 SDRAM需要的0.75V终端电压和0.75V参考电压。

读出模块硬件设计的挑战包括DDR3 SDRAM接口。DDR3 SDRAM选用SAMSUNG公司的K4B2G1646C-HCK0[6]。该DDR3芯片属于SAMSUNG第四代DDR产品,具有2 Gbit的存储空间,最高支持800MHz的物理时钟,即1600Mb·s-1的DDR数据率。每片芯片内部共有16个bank,每个bank有128Mb的存储空间,使用96ball的FBGA (Fine-Pitch Ball Grid Array)封装,易于扩展。XC7Z010的DDR3接口可以高达533MHz,考虑到DDR接口的特性,其实接口速度已经达到了1066MHz,每个数据读取的窗口约为1ns。因此,DDR3 SDRAM接口的PCB布线非常关键,ZYNQ系列的DDR3接口需要40Ω阻抗匹配,同时,每个数据线组,比如D0~D7以及DQS0_P、DQS0_N、DQM0;D8~D15以及DQS1_P、DQS1_N、DQM1在组内应该控制等长,误差限在0.127mm内。

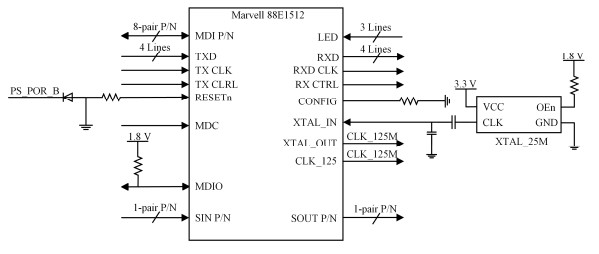

千兆以太网接口使用Marvell公司的RGMII (Reduced Gigabit Media Independent Interface)接口的物理层芯片88E1512,最大的好处是这颗PHY (Physical Layer)芯片和XC7Z010使用同样的电源,也需要1.0V、1.8V和3.3V,可以降低电源的设计难度。另外这颗PHY芯片不但能使用非屏蔽双绞线接口,也能支持光纤接口,非常灵活,图 3是PHY芯片的接口原理图。

|

图 3 以太网接口原理图 Figure 3 Schematic of gigabit Ethernet interface |

ZYNQBee模块的启动过程较为复杂,主要是涉及内部的ARM处理器和FPGA的启动过程[7]。在ZYNQ系列处理器内部,有一块固化的BootROM,上电复位以后,ZYNQ处理器先执行BootROM内部的固化代码、初始化必须的时钟和IO接口,同时根据某些配置IO的上拉与下拉状态,来选择进一步加载启动代码的设备,包括QSPI、SD卡、NAND Flash、NOR Flash或者JTAG。

存储在启动介质中的启动镜像,被BootROM加载到内部RAM或者DDR3 SDRAM中运行,这个启动镜像被称为FSBL (First Stage Boot Loader)。整个FSBL可以在Xilinx公司的Vivado SDK下编译修改,用户可以根据自己的需求做修正和定制。FSBL启动以后,就会从启动介质读取SSBL (Second Stage Boot Loader),而SSB可以是u-boot等通用的开源bootloader,下面的开发环节与其他嵌入式系统的开发没有太大区别。

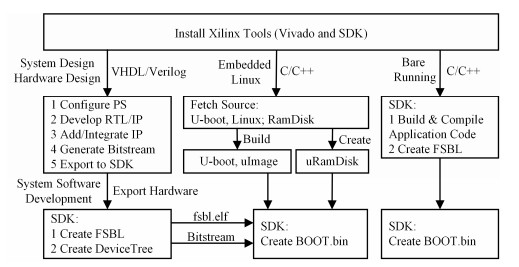

ZYNQ系统是集成了处理器内核和FPGA的SoC,那么整个软件的开发就包含基于C语言的程序开发和基于VHDL/Verilog语言的逻辑开发,整个设计流程图如图 4所示。首先需要在Vivado环境下配置PS的参数,以IP Block的方式进行开发、设计或者构建各个功能模块,先后通过仿真验证、综合、布线,最终生成Bitstream文件。其次,将生成的文件和相关配置信息导入SDK中。

|

图 4 ZYNQ的开发流程图 Figure 4 Flow chart of ZYNQ development |

当涉及嵌入式Linux开发时,可在交叉编译环境下编译或创建u-boot、uImage(Linux镜像文件)以及uRamDisk(Linux文件系统),并在SDK下创建FSBL、DeviceTree文件,最终创建BOOT.bin文件,可通过JTAG烧录至QSPI FLASH中。也可以在SDK下先进行Program FPGA操作,再通过JTAG加载BOOT.bin,启动u-boot。在u-boot下,对QSPI FLASH可进行擦写操作。启动嵌入式Linux以后,用户可以使用NFS (Network File System)以及交叉编译环境来调试应用程序。

当不涉及操作系统开发时,此时的开发方式和实现功能相对简单。在SDK下创建和开发用户的应用程序,并创建FSBL文件,最终创建得到BOOT.bin文件。

3 ZYNQBee在CDEX高纯锗探测器数据采集系统中的应用CDEX是国内完全自主的暗物质直接探测实验,计划利用吨量级的点电极高纯锗探测器开展暗物质直接探测和无中微子双β衰变的实验研究[8]。

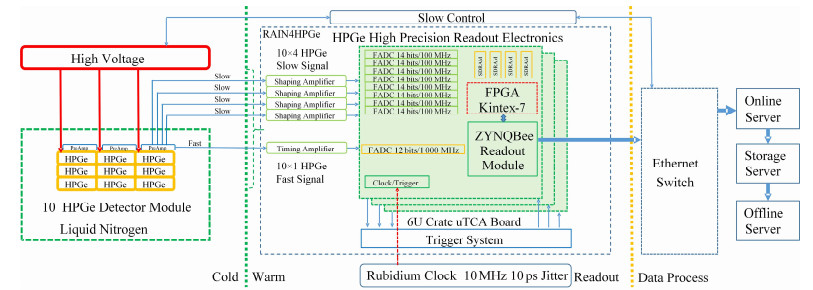

图 5为目前CDEX电子学系统的基本框图。CDEX电子学包括前端电子学、触发系统和数据采集系统三部分[9]。前端电子学主要为前置放大器和成形电路;触发系统包括触发和时钟分布系统;数据采集系统包括数据读出电子学、慢控制电子学以及相关的数据服务、存储、通信、显示和人机接口等。数据采集系统板卡RAIN4HPGe (Data Acquisition System, DAQ)设计的8通道14 bit 100MHz高速ADC和2通道12 bit 2 GHz高速ADC用于波形采样,Kintex-7系列的FPGA用于快速模数转换器(Fast Analogue Digital Converter, FADC)数据的获取,与Kintex-7 FPGA相连接的4片256MB DDR3 SDRAM用于数据的高速缓存[10]。在触发信号下,Kintex-7 FPGA将数据传送给ZYNQBee模块,经ZYNQBee的FPGA设计和嵌入式Linux的开发,实现了将板卡中ADC采集的数据最终经千兆以太网口传输至虚拟机服务器,实物图如图 6所示。

|

图 5 CDEX电子学系统的基本框图 Figure 5 Block diagram of CDEX electronic system |

|

图 6 数据采集系统板卡的实物照片 Figure 6 Picture of DAQ |

下面具体介绍ZYNQBee上的设计过程。

首先,需要实现的是DAQ与ZYNQBee的数据传输。在DAQ设计中,将Kintex-7 FPGA中的12对支持LVDS (Low Voltage Differential Signaling)标准的引脚(其中包括3对时钟引脚)通过差分线与ZYNQBee的底板插槽相连接。设计中采取了类似ADC接口的时钟、使能和数据的形式实现数据传输。设计有1对100MHz差分时钟线、1 bit控制线和16 bit的数据线。时钟线选择了LVDS25电平标准,其余选择了LVCMOS25的电平标准。

其次,在Vivado下配置PS的时钟、DDR SDRAM、UART等外设接口,通过PL设计,实现数据的FIFO缓存,数据写入双口Block RAM以及通过DMA接口将数据由Block RAM传输至ZYNQBee读出模块外部的DDR3 SDRAM中。经设计、优化后,最终生成Bitstream文件。将其导出至SDK中,通过创建工程和板级支持包分别得到FSBL文件和DeviceTree配置文件。在虚拟机ubuntu下建立交叉编译环境,将DeviceTree配置文件编译生成二进制文件,同时创建和编译嵌入式Linux开发所需的u-boot等文件。整个ZYNQBee模块运行u-boot 2014.01版本以及嵌入式Linux 3.13.0版本。

最后,通过C/C++开发嵌入式Linux程序,其包括TCP/IP客户端的建立、CDMA (Central Direct Memory Access)的寄存器配置等。设计中采取连续触发模式,将数据通过DMA接口缓存到外部的DDR3 SDRAM中,整个过程不再需要CPU的参与。同时通过C/C++开发ubuntu下的应用程序,基本功能包括TCP/IP服务器端的建立、数据的存储及显示等。服务器与客户端之间采用TCP/IP socket通讯,其开发简洁,有成熟的函数接口可供调用。

设计框图如图 7所示,图中使用虚线箭头表示数据流向。

|

图 7 ZYNQ在DAQ模块应用框图 Figure 7 Block diagram of ZYNQBee used in DAQ |

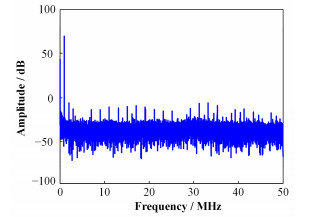

实验中,我们测试了FADC的有效位数以及千兆以太网的平均速度等。我们选用Tektronix AFG3252C型号的信号发生器,其DAC精度为14bit 5Vp-p, 令其产生1MHz 1 Vp-p的正弦波,测试DAQ上100MHz 14bit AD9253的有效位数(Effective Number of Bits, ENOB)。Unbuntu服务器将每次接收到的64KB数据(共32768个ADC数据)写入文件并保存。我们选用了ADI公司的VisualAnalog计算得到信噪比61.92dB,最终计算得到ADC的有效位数约为(61.92-1.763)/6.02= 10bit。图 8是根据FADC采集到的数据,通过快速傅氏变换(Fast Fourier Transformation, FFT)绘制而成的频谱图。表 2为计算得到的ADC常见参数。

|

图 8 1MHz 1Vp-p正弦波测试AD9253的频谱 Figure 8 Spectrum of AD9253 sampling 1MHz 1Vp-p sine wave |

| 表 2 AD9253的参数测试结果 Table 2 Test result of AD9253's parameters |

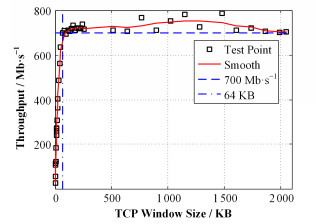

此外,为了测试千兆以太网的平均速度,我们使用iperf3网络带宽性能测试工具。实验中,令虚拟机ubuntu作为主机,ZYNQBee作为客户端,并将二者通过千兆以太网交换机接入至同一局域网中,在iperf3的普通测试模式下,得到了ZYNQBee千兆以太网口的数据传输速率随不同TCP窗口大小的变化曲线,如图 9所示。当TCP窗口大小约在64KB以上时,千兆以太网数据传输的平均速率超过了700 Mb·s-1。

|

图 9 千兆以太网的带宽测试 Figure 9 Test of Gigabit Ethernet bandwidth |

1) ZYNQ实现了FPGA (PL)和处理器(PS)间的高带宽数据传输。一般来讲,FPGA和处理器可以通过Local Bus或者PCI Bus来进行数据交换,但是带宽都不是很理想,常见的Local Bus是32位宽度、60MHz的时钟速度。而ZYNQ内部的处理器和FPGA逻辑单元之间有4路固定的高性能高带宽支持DMA的数据通道,可以达到64位宽度及超过150MHz时钟速度,即达到1.2GB·s-1的带宽,并且每个通道拥有1KB的FIFO,极大地提高了处理器和FPGA之间数据交换的速度,使得数据交换不再成为瓶颈。

2) 整个ZYNQBee模块具有很好的适用性。系统的FPGA引出了约27对高速差分的LVDS信号,可以达到1250Mb·s-1的DDR接口速度,可以非常方便与高速ADC、DAC芯片接口。

3) 新型架构的ZYNQBee读出模块使得核电子学读出系统的带宽和性能达到了一个新的高度,大大减小了核心尺寸和功耗,提高了读出性能,可以广泛应用在核电子学数据获取系统中的读出单元。初步测试下,TCP窗口大小在64KB以上时,千兆以太网的平均速度可以达到700Mb·s-1以上。ZYNQBee已成功地应用于CDEX电子学系统的读出,同时为系统ADC的性能测试提供了便利。

| [1] |

刘书魁, 岳骞. 直接探测暗物质和中国暗物质实验[J]. 物理, 2015, 44(11): 722-733. LIU Shukui, YUE Qian. Dark matter direct detection and China dark matter experiment[J]. Physics, 2015, 44(11): 722-733. DOI:10.7693/wl20151103 |

| [2] |

Dufey J P, Frank M, Harris F. The LHCb trigger and data acquisition system[J]. IEEE Transactions on Nuclear Science, 2000, 47(2): 86-90. DOI:10.1109/23.846123 |

| [3] |

Zynq-7000 all programmable SoC overview (DS190)[EB/OL]. 2015-3-1. https://www.xilinx.com/support/documentation/data_sheets/ds190-Zynq-7000-Overview.pdf.

|

| [4] |

TPS6213x 3-V to 17-V, 3-A step-down converter in 3x3 QFN package[EB/OL]. 2015-3-2. http://www.ti.com/lit/ds/symlink/tps62130.pdf.

|

| [5] |

TPS51206 2-A peak sink/source DDR termination regulator with VTTREF buffered reference for DDR2, DDR3, DDR3L, and DDR4[EB/OL]. 2015-3-3. http://www.ti.com/lit/ds/symlink/tps51206.pdf.

|

| [6] |

Product guide of consumer memory[EB/OL]. 2015-3-2. http://www.samsung.com/global/business/semiconductor/file/product/consumer_product_guide_nov_12-0.pdf.

|

| [7] |

Overview of the Xilinx Zynq UltraScale+ MPSoC & Zynq-7000 AP SoC design flow[EB/OL]. 2015-3-3. http://www.wiki.xilinx.com/Getting+Started.

|

| [8] |

岳骞. 高纯锗探测器在粒子物理与天体物理中的应用[J]. 中国科学:物理力学天文学, 2011, 41(12): 1434-1440. YUE Qian. The application of high purity germanium detector in particle and astroparticle physics[J]. Science China Physics, Mechanics & Astronomy, 2011, 41(12): 1434-1440. DOI:10.1360/132011-965 |

| [9] |

Kang K J, Cheng J P, Li J. Introduction to the CDEX experiment[J]. Frontiers of Physics, 2013, 8(4): 412-437. DOI:10.1007/s11467-013-0349-1 |

| [10] |

Xue T, Gong G, Li J. Combo FADC readout system with 8-channel 14-Bit 100 MHz FADC and 2-channel 12-Bit 2GHz FADC for HPGe detector[C]. IEEE Nuclear Science Symposium and Medical Imaging Conference, San Diego, California, US, 2015.

|