2. 信息内容安全技术国家工程实验室, 北京 100093;

3. 北京特种工程设计研究院, 北京 100028

2. National Engineering Laboratory of Information Security Technologies, Beijing 100093, China;

3. Beijing Special Engineering Design and Research Institute, Beijing 100028, China

随着计算机和Internet技术的迅速发展,网络信息技术日益深入社会、经济、政治、民生的方方面面,使人们的生活和工作越来越离不开网络通信; 然而,现代社会的人们面临着信息窃听、信息伪造、信息重放等多种信息安全方面的巨大隐患, 因此,伴随而来的信息传输安全问题也引起了学者们的高度关注。信息安全的主要内容是保护信息和承载信息的载体,避免信息和信息系统遭受任意形式的破坏和攻击; 一旦信息和信息系统受到攻击和破坏,应能迅速响应、阻断破坏、修复信息和信息系统。在实际应用中,信息安全的解决主要依靠两种方式:以“防火墙”技术为核心的被动防御系统和以“密码”为基础的主动保障系统。密码技术作为保护信息安全的最重要方式之一,在保护信息系统安全方面有着举足轻重的地位。信息加密以某种特殊的算法改变原有的信息数据,使得未授权的用户即使获得了已加密的信息,但因不知解密的方法,仍然无法了解信息的内容,从而对信息进行保护。

美国国家标准与技术研究院 (National Institute of Standards and Technology, NIST) 在1997年便宣布了一个高级加密标准 (Advanced Encryption Standard, AES) 的开发工作以代替已经力不从心的数字加密标准 (Data Encryption Standard, DES)。而最终,由Joan Daemen和Vincent Rijmen设计的Rijndael算法[1]被选择为AES算法。对于目前密码算法的高速性能要求,尤其是数据传输速度达到GB数量级时,密码算法的硬件实现便显得尤为重要。以现场可编程门阵列 (Field-Programmable Gate Array, FPGA) 为代表的可重构硬件以其自身所固有的特点——既具有硬件的安全性和高速性又有软件的灵活性和易维护性,已经成为分组密码算法硬件实现的热点研究方向[2]。

文献[3]总结了目前传统开发方法遇到的问题以及使用高层次综合 (High-Level Synthesis, HLS) 技术的优势,即由于在片上系统 (System on a Chip, SoC) 上创建更多更复杂的应用,其功能设计的复杂度也随之增加,而且还要考虑功耗控制以及工艺变化等问题。然而利用HLS技术可以自动化管理这些日益增加的复杂设计,让设计开发人员专注于高层功能的设计以及非常便捷地探索设计空间以优化设计。目前的一些高层次综合工具支持从C/C++代码进行硬件综合。使用这些高层次综合工具的优势也是十分明显的,这将给硬件设计开发带来更高的效率,并能够充分利用已有的可靠软件程序,减少开发成本与时间[4]; 然而,并不是所有的C/C++代码都能够直接用于硬件设计, 因此需要在C/C++设计层面上作出改变以达到高效的硬件设计实现,比如文献[5]探讨了基于HLS技术,在低资源情况下随机存取存储器 (Random Access Memory, RAM) 不同分割数目对于AES算法的性能的影响; 文献[6]则探讨了算符、操作相关带来的影响; 文献[7]基于HLS技术利用C到寄存器传输级 (C to Register-transfer level, C2R) 设计方法探索设计空间,以设计不同硬件结构的AES算法来满足不同的性能资源需求的实现; 文献[8-11]探讨了传统设计方法下对于AES算法的硬件设计,其中的文献[8]利用了GF(24) 上的多项式表示来替换AES原始的GF(28) 上的计算以提高硬件流水吞吐量。还有应用于主干网的AES高性能硬件设计研究[12-15]。

利用HLS技术可以非常方便地实现与优化AES算法硬件设计; 然而,目前却缺乏对于全自动优化与手动优化对于最终性能的影响的分析, 也缺乏对于代码映射出的硬件结构的分析, 这对于进一步改善性能,减少资源消耗是不利的。在本文中描述了关于AES算法基于C的软件设计以及其硬件实现结构,本文依次给出了三种不同代码设计以及优化方法,并分别添加流水线优化得到其最终性能资源情况,分析其映射的总体硬件结构同时也对比分析不同的优化策略效果,最终得到了高性能、资源利用低的设计版本。

1 背景介绍 1.1 高级加密标准AES高级加密标准,在密码学中又称Rijndael加密算法,是美国联邦政府采用的一种区块加密标准。这个标准用来替代原先的DES,已经被多方分析且广为全世界所使用。其分组长度为128位,而使用的密钥长度可以为128位、192位或256位,即AES算法分为AES-128、AES-192和AES-256,由于彼此之间的相似性,本文只描述并实现了AES-128加密算法,更多细节可以参考文献[16]。

大多数AES计算是在一个特别的有限域完成的。AES加密过程是在一个4×4的字节矩阵上运作,这个矩阵又称为“状态 (state)”矩阵,其初值就是一个明文区块 (矩阵中一个元素大小就是明文区块中的一个Byte)。加密时,各轮AES加密循环 (除最后一轮外) 均包含4个步骤:

轮密钥加 (AddRoundKey) 矩阵中的每一个字节都与该次轮密钥 (Round Key) 做XOR运算;每轮子密钥由密钥生成方案产生。

字节代换 (SubBytes) AES中的字节代换往往用查找表的方式把每个字节替换成对应的字节。即定义了一个S盒与逆S盒。S盒用于加密过程的字节代换,逆S盒用于解密操作的逆字节代换。对于状态矩阵中的元素,将其高4位作为行值,低4位作为列值,取出S盒或逆S盒中对应的元素作为输出。

行移位 (ShiftRows) 将矩阵中的每行进行循环式移位。即状态矩阵的第0行左移0字节,第1行左移1个字节,第2行左移2个字节,第3行左移3个字节。这就使得每一列完全重排了。

列混合 (MixColumns) 为了充分混合矩阵中各个直行的操作。这个步骤使用线性转换来混合每列的四个字节。状态矩阵中的第j列 (j= 0, 1, 2, 3) 的列混合如下表示为:

| $ \left\{ \begin{array}{l} {{s'}_{0,j}} = (2 \cdot {s_{0,j}}) \oplus (3 \cdot {s_{1,j}}) \oplus {s_{2,j}} \oplus {s_{3,j}}\\ {{s'}_{1,j}} = {s_{0,j}} \oplus (2 \cdot {s_{1,j}}) \oplus (3 \cdot {s_{2,j}}) \oplus {s_{3,j}}\\ {{s'}_{2,j}} = {s_{0,j}} \oplus {s_{1,j}} \oplus (2 \cdot {s_{2,j}}) \oplus (3 \cdot {s_{3,j}})\\ {{s'}_{3,j}} = (3 \cdot {s_{0,j}}) \oplus {s_{1,j}} \oplus {s_{2,j}} \oplus (2 \cdot {s_{3,j}}) \end{array} \right. $ | (1) |

AES算法中还包括密钥拓展 (KeyExpansion) 操作。其为每一个轮密钥加操作提供轮密钥。首先,将初始密钥输入到一个4×4的字节矩阵上,然后将每一列4个字节的元素组成一个字,于是便形成了数组w。对于AES-128算法而言,要将w扩充40个新列,构成44列的拓展密钥数组。其计算过程为:

| $\left\{ \begin{array}{l} w[4i] = w[4i-4] \oplus (RotWord(SubWord(w[4i\\ -1])) \oplus Rcon[i])\\ w[4i + 1] = w[4i] \oplus w[4i-3]\\ w[4i + 2] = w[4i + 1] \oplus w[4i-2]\\ w[4i + 3] = w[4i + 2] \oplus w[4i-1] \end{array} \right. $ | (2) |

其中:RotWord表示字循环的功能,即将这个字的循环左移1个字节;SubWord是对字进行字节代换操作;Rcon为轮常量数组。

1.2 现场可编程逻辑门阵列FPGA是一类高集成度的可编程逻辑器件,起源于美国的Xilinx公司,可以用硬件描述语言 (Hardware Description Language,HDL) 来编程,它灵活性强,不仅能够进行编程、除错、可重复擦写操作,还可以结合算法的特点和硬件的结构进行重构,提高了系统的可升级性和产品的市场寿命。

FPGA由基本可编程的逻辑单元、可编程I/O的单元、嵌入式块RAM、布线资源等重要部分构成。FPGA器件及其系统开发利用计算机软件,绘制出实现用户逻辑的原理图或用硬件描述语言等方式作为设计输入,然后经过一系列转换程序、自动布局布线、模拟仿真的过程,最后生成配置FPGA器件的数据文件,下载到FPGA器件中,从而实现了满足用户需求的专用集成电路,真正达到了用户自行设计集成电路的目的。其一般通过自顶向下的设计方法,实现设计的结构化,使一个复杂的系统设计可由多个设计者分工合作,同时还可以实现层次化的管理[17]。其自顶向下的设计流程包括设计定义、HDL实现、功能仿真、逻辑综合、前仿真、布局布线、后仿真、静态时序分析、系统测试9个步骤[18]。

1.3 高层次综合HLS是指采用高层次语言,比如C或者C++描述底层的数字设计。显然,它能让设计师和工程师在较高的抽象层面上完成底层设计。利用HLS能快速探索各种方案的可能性,分析资源面积和性能特点,最终确定硬件芯片上算法实现方案。

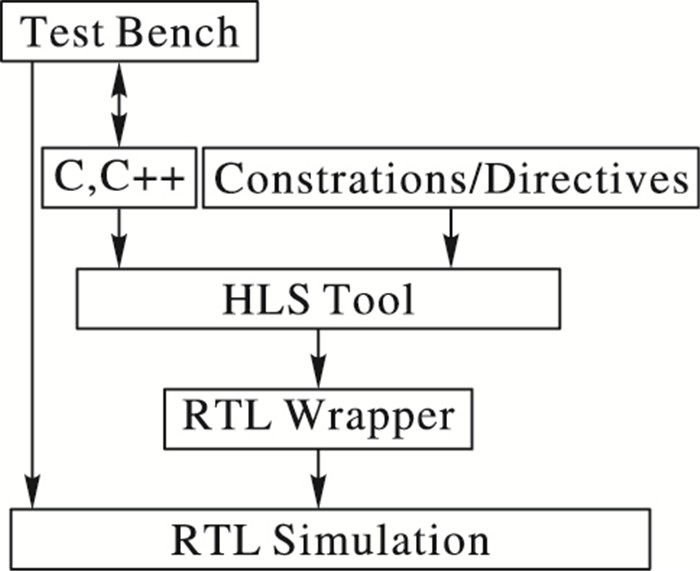

如图 1HLS流程,用户先创建一份C、C++算法设计文件,以及一个用于测试系统行为的Test Bench; 随后用高层语言的仿真器验证设计的系统行为, 一旦算法设计的运行结果正确,就可以通过HLS运行设计,生成RTL (Register-Transfer Level) 级别的设计,代码可以是硬件描述语言Verilog或者VHDL。有了RTL设计之后,随即可以执行设计的硬件仿真。

|

图 1 HLS流程 Figure 1 Flow of HLS |

不仅如此,HLS提供的抽象层次有助于开发人员从高层设计硬件逻辑,解决了常见硬件系统设计难题,最终简化系统汇编,简化FIFO (First Input First Output) 和存储器访问;此外,HLS提供了指令完成架构研究功能,也就是Constrains/Directives部分,设计者可以通过添加插入程序指令,把设计所需特性传递给综合工具, 这样就可以在不修改设计代码本身的情况下研究大量备选架构方案。

算法的设计工作基于HLS,主要完成Test Bench、C/C++以及Constrains/Directives部分的设计。Test Bench模拟未来系统中的软件部分,也充当测试硬件设计的角色;而C/C++部分经过RTL设计后,就是未来系统中的硬件部分;Constrains/Directives是开发人员在设计C/C++部分时,考虑采用的优化手段,能够指引硬件代码资源的利用、并行的设计等。这样从整体上完成了软硬件的协同设计,统筹设计了整个系统,有助于挖掘硬件更大的计算能力。

2 算法实现 2.1 基准代码设计利用HLS技术就可以像软件设计人员开发软件一样通过编写C/C++代码来达到FPGA硬件设计的目的。此时,像平时编写C程序一样,首先,编写出第1版AES-128加密模块的C代码, 其伪代码简要描述如下:

方法名 aes_enc_v1。

输入 indata,initkey;

输出 outdata。

1) if未进行过密钥拓展

2) keyExpansion (initkey);

3) endif

4) 初始化状态矩阵state并对其对做轮密钥加;

5) for round=1 to 9

6) subByte (state);

7) shiftRow (state);

8) mixColumn (state);

9) 对状态矩阵state做轮密钥加;

10) endfor

11) subByte (state);

12) shiftRow (state);

13) 对状态矩阵state做轮密钥加;

14) 输出结果outdata。

首先,大体上说明一下代码的实现。对于函数keyExpansion,其输入初始密钥initkey,然后进行密钥拓展的操作,再将44列的结果放入数组key中。当然,这个密钥拓展操作只需要在开始时计算即可,对于后续需要加密的128比特块可以一直使用先前的密钥直到需要更改密钥时。

密钥拓展操作完成以后,就是AES-128加密算法的具体流程。首先,在第0轮首先对状态矩阵state对每一个元素与此轮轮密钥进行异或操作,很显然,状态矩阵state在代码中是以数组形式存在的,而与之异或的轮密钥也是存储在数组中,很自然地轮密钥加的过程是用一个循环来实现的。循环在软件程序设计中是十分常用的结构,而且正因为循环的使用,软件开发人员可以编写十分简练的代码,大大提高软件开发效率,并且,本研究在这一版代码中像平时编写C代码一样许多地方使用循环操作。

第0轮操作以后,就是第1轮到第9轮的加密过程,除了轮密钥加的操作以外,还包含字节代换、行移位以及列混合操作。这三个操作都是通过函数调用的形式完成的。函数调用也是平时常用的方法,利用函数调用可以逐步地解决算法任务,而且还可以利用许多高效的系统函数来帮助编写C/C++程序,进而提高程序开发的效率。因此,本文在这一版的程序中也将一些加密操作以函数调用的形式实现。

对于字节代换函数subByte,其输入是状态矩阵state,在这个过程中,本研究使用查表的方式实现的,即函数中通过查找S盒来完成字节代换操作,而不是通过计算得到的。行移位函数shiftRow,输入是state,进行的操作如同上一章节描述的那样进行。列混合函数mixcolumn输入为state,其实现的方式与上一章节描述的过程略有不同,其并没有乘法运算过程,而是将乘法运算的结果都放入到两个数组mm02和mm03中,前者是元素与0x02相乘的所有结果的集合,后者是元素与0x03相乘的结果集合。因此,实际上列混合操作只有异或运算了。当然,在这个函数中也用到了循环结构。

第10轮调用函数subByte完成字节代换,接着调用函数shiftRow完成行移位,最后再做一次轮密钥加的操作完成了一个128比特块的整个加密过程。

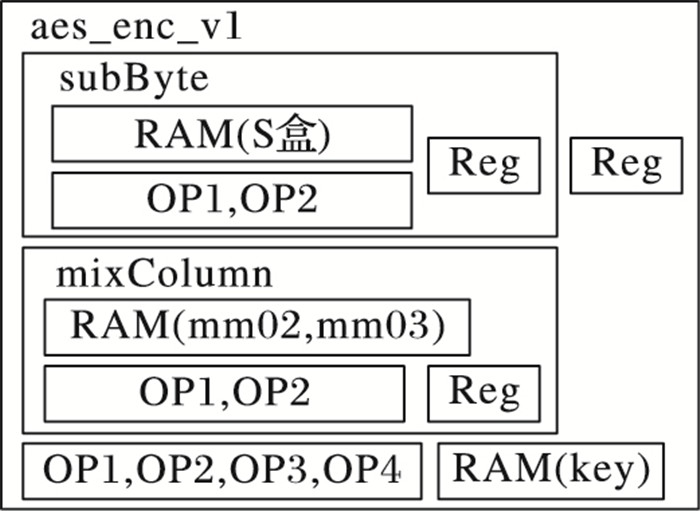

完成了软件设计以后,就要对软件代码进行C语言功能仿真以验证功能的正确性,完成高级语言功能验证以后,就可以利用HLS工具综合出RTL级设计,即本文所设计的硬件部分。首先,对于第1版的代码主要加密操作对应的结构如图 2所示。在HLS工具综合过程中,数组时常被映射为RAM结构,运算式则利用LUT (Look Up Table) 构造。在aes_enc_v1这个顶层模块中,HLS工具一般会将子函数单独生成一个子模块,若是子函数非常简单,HLS工具会自动将其内联到顶层函数中。对于方法aes_enc_v1所映射出的结构,可以看出,受限于循环和子函数的限制,整体并行运算程度不高,HLS工具也就不会分配更多的可访问资源,因此,子模块与顶层模块之间以及子模块与RAM之间的通信会是十分频繁的,这就带来更多的延迟了。

|

图 2 aes_enc_v1方法硬件模块结构 Figure 2 Hardware module structure of aes_enc_v1 |

上述的第1版的代码可以说是一个非常常见的C代码设计。然而,事实上从硬件设计的角度而言是并非是一个很高效的方法。因此,可以对代码进行改写,而第2版AES-128加密模块的C代码的伪代码如下所示:

方法名 aes_enc_v2。

输入 indata,initkey;

输出 outdata。

1) if未进行过密钥拓展

2) keyExpansion (initkey);

3) endif

2) 初始化状态矩阵state;

2) 对状态矩阵state进行轮密钥加;

2) for round=1 to 9

2) 对状态矩阵state进行行移位;

2) 对状态矩阵state进行字节代换;

2) 对状态矩阵state进行列混合与轮密钥加;

2) endfor

2) 对状态矩阵state进行行移位;

2) 对状态矩阵state进行字节代换与轮密钥加;

13) 输出结果outdata。

在这一个版本的代码中,与前一个版本最大的不同在于把加密操作的函数代码都写在顶层函数中,并且,除此之外,还把加密操作中的循环全部展开了,只保留有1到9轮加密操作的主循环。将循环展开是一种非常自然的优化方法,将循环展开之后,就可以发现表达式之间其实并不存在任何相关关系,此时就可以并行处理了,而不像先前受限于循环只能串行操作;而且又打破了函数之间界限,可以进一步提高并行处理的能力以提高数据吞吐量,而且也能优化资源的利用。

对于字节代换过程而言,状态矩阵中的每一个元素通过S盒来进行替换。事实上,每个元素的替换过程没有任何依赖关系,可以完全并行执行。而对于行移位操作而言,其在传统设计中只需要改变连线就可以达到效果,而在本研究的设计中,只需要在字节代换过程中改变元素的赋值顺序就可以了。对于列混合操作,从式 (1) 可以看出,状态矩阵每一个新元素依赖于同一列的四个旧元素。因此,每一个新元素的计算是可以完全并行执行的。因此,循环展开是完全可以提高性能的。

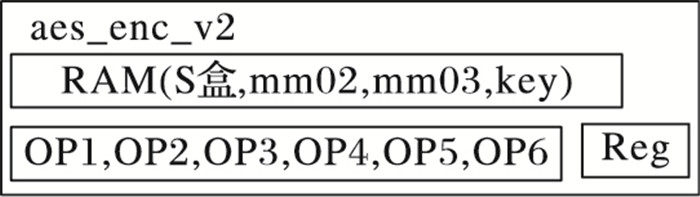

aes_enc_v2方法所映射的总体结构如图 3所示。正如之前所言,在方法aes_enc_v2中,打破了循环与函数之间界限,而且,事实上AES算法本身具有非常良好的并行执行能力,许多表达式之间并没有相关关系,完全可以并行处理,之前循环的串行执行则会强迫产生不必要的等待时间,增加整个加密过程的延时。由于此时打破了循环与子函数的限制,HLS工具可以在更广的范围内对一系列的操作进行调度优化,可以进一步提高AES加密算法的并行执行能力,从而进一步降低整个加密过程的延时与资源占用情况。

|

图 3 aes_enc_v2方法硬件模块结构 Figure 3 Hardware module structure of aes_enc_v2 |

上述的两个版本的代码在很大程度上是依赖于表的查找,因为已经事先就计算好了一些运算操作的结果并存储在数组中, 而数组往往会被映射成RAM结构。对于RAM块的需求会很大,而且频繁访问RAM块会增加路径延时,从而影响硬件的工作时钟频率[15],这对于进一步提升算法实现的性能是不利的。事实上,本文还可以对aes_enc_v2的列混合部分的代码进行改写。在域上的乘法乘以0x02等价于下列的结果:

| $ \left\{ \begin{array}{l} {a_6}{a_5}{a_4}{a_3}{a_2}{a_1}{a_0}0{\rm{ }}, \;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;{a_7} = 0\\ {a_6}{a_5}{a_4}{a_3}{a_2}{a_1}{a_0}0 \oplus 00011011{\rm{ }}, {a_7} = 1 \end{array} \right. $ | (3) |

因此,基于方法aes_enc_v2所做的改进而得到新一版的C语言算法设计。将这个第3版方法命名为aes_enc_v3。

对于aes_enc_v3方法映射成的硬件结构与图 3并没有什么太大的不同,只是资源占用的情况不太一样,其显然要比aes_enc_v2方法的RAM少,但是由于运算增加,对LUT资源需求会增加一些。

2.4 流水线优化本文的目标是追求高性能算法实现,因此有必要进一步提高数据吞吐率, 故必须要给硬件结构增加流水线设计以进一步提高吞吐量。而此时,可以利用HLS工具自带的命令来帮助完成想要的硬件结构设计。本文利用HLS工具的流水线命令对aes_enc_v1、aes_enc_v2与方法aes_enc_v3进行流水线的优化;然后,增加流水线的设计可以大幅地增加硬件设计的吞吐量,利用流水线优化会自动展开循环进行优化调整,这样可以进一步提高硬件实现的并行执行的能力,因此整个加密过程的延迟也可以进一步降低,当然,这会导致更大的资源占用情况。

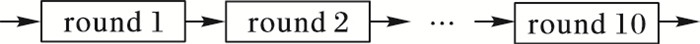

图 4是设计aes_enc_v1第1轮到第9轮轮内的结构,而第10轮结构与其类似,只是少了列混合操作。

|

图 4 aes_enc_v1轮内流水结构 Figure 4 Pipeline structure of aes_enc_v1 in one round |

图 5是设计aes_enc_v1整个实现结构。对于方法aes_enc_v2与方法aes_enc_v3而言,其轮内轮外操作已经都糅合在一起。虽然总体操作过程与原始方法aes_enc_v1相同,然而其某些操作过程的顺序已经被高层次综合工具自动调度了。

|

图 5 aes_enc_v1整体流水结构 Figure 5 Overview of pipeline structure of aes_enc_v1 |

本研究使用Vivado集成开发环境中的HLS工具完成本文中的设计。实验采用的FPGA器件是xc7z020clg484-1。首先对aes_enc_v1方法、aes_enc_v2方法和aes_enc_v3进行硬件综合以了解其性能和利用情况。表 1描述的是三种设计的性能评估。表 2描述的是三种设计的资源利用情况 (注:BRAM为Block RAM,FF为Filp-Flop,DSP为Digital Signal Processing,LUT为Look-Up Table)。

| 表 1 三种设计性能评估 时钟周期 Table 1 Performance evaluation of three designs clock cycle |

| 表 2 三种设计资源占用情况 Table 2 Resource occupancy of three designs |

实验中FPGA的时钟约束均为100 MHz。方法aes_enc_v1受限于循环与子函数的限制,导致并行执行的能力没有很好地发挥出来,因此比后两者的延时要大很多。从表 1可以看出,aes_enc_v1的延时是后两者的11.7倍, 而方法aes_enc_v1与方法aes_enc_v2的延迟此时是一样的。

此时再来查看三种设计对于资源的占用情况:方法aes_enc_v1的对资源的占用从总体上看是最高的; 方法aes_enc_v2比方法aes_enc_v1在BRAM方面少用3块RAM,在FF方面比其减少12.2%的资源使用,在LUT方面比其减少24.2%的资源使用;方法aes_enc_v3比方法aes_enc_v1在BRAM方面少用7块RAM,在FF方面比其减少16.4%的资源使用,在LUT方面比其减少3.8%的资源使用; 而方法aes_enc_v2与方法aes_enc_v3在有相同的资源利用。

综合表 1与表 2的实验结果分析,方法aes_enc_v1的设计效果并不理想,不仅延时很高,而且资源的占用也是3种设计之中最高的。对于方法aes_enc_v2与方法aes_enc_v3来说,其无论是性能上还是资源占用上并没有太大的不同,而之前预计方法aes_enc_v3要比方法aes_enc_v2延时要更低一些。这是因为受限于主循环的限制,加密模块整体并行执行能力依旧受到了许多限制,访问RAM所带来额外的延时依旧有许多可以缓和的额外空间。总的来看,对于方法aes_enc_v1所进行的优化设计符合要求,达到了预期的效果。

然后,此时来查看对于方法aes_enc_v1、aes_enc_v2与aes_enc_v3进行流水线优化后其性能情况以及资源利用情况。表 3描述的是三种设计进行流水优化的性能情况。表 4描述的是三种设计进行流水优化后的资源利用情况。

| 表 3 流水线优化后性能评估 时钟周期 Table 3 Performance evaluation with pipelining clock cycle |

| 表 4 流水线优化后资源占用情况 Table 4 Resource occupancy with pipelining |

从表 3可以看出,添加了流水线之后,加密模块的延时与吞吐量得到了很大的改进。方法aes_enc_v1流水线优化后的延时为原先的1.6%,方法aes_enc_v2流水线优化后的延时为原先的28.3%,而方法aes_enc_v3流水线优化后的延时仅为原先的19.2%。从吞吐量方面来看,对于方法aes_enc_v2与aes_enc_v3而言,若时钟频率均相同的情况下,进行流水线优化后其吞吐量是之前的100倍。对于方法aes_enc_v1而言则是1 157倍,而这也意味着与原始的基准设计相比,最终的性能提升了3个数量级。另外,可以看到方法aes_enc_v2与方法aes_enc_v3在延时上的区别,后者的延时比前者减少了32.1%。虽然方法aes_enc_v2申请了大量RAM资源以提高并行执行效率,减少资源冲突带来性能损失,然而频繁访问RAM会增加延迟,从而影响加密模块的工作频率,这降低了硬件的吞吐量。其次,三种设计Interval均为1,也就意味着每个时钟周期都可以输入数据进行运算处理。事实上,当达到全流水线的架构时,吞吐量仅仅取决于时钟频率[8],其计算公式为:

| $ throughput = blocksize \times frequency $ | (4) |

从表 4可以看出,进行流水线优化后,对资源利用需求大幅提高。对于方法aes_enc_v1而言,进行流水线优化后对于RAM块的需求是原先的24.4倍,对FF资源的需求是原先的17.7倍,对LUT的需求是原来的5.6倍;对于方法aes_enc_v2而言,进行流水线优化后对于RAM块的需求是原先的34.9倍,对FF资源的需求是原先的4.3倍,对LUT的需求是原来的5.7倍;对于方法aes_enc_v3而言,进行流水线优化后对于RAM块的需求是原先的33.3倍,对于FF的需求是原先的3.0倍,而对于LUT资源的需求是原来的7.0倍。

对于完全依赖于高层次综合工具进行优化的方法aes_enc_v1而言,其最终性能非常优越。其延时与方法aes_enc_v3相同,比方法aes_enc_v2还要低。这也说明过多地将逻辑内联进顶层模块事实上会降低性能。当然,此时可以看到方法aes_enc_v1对于资源的占用从总体上看是最大的。

综合来看,虽然此时资源需求提高很多,然而,性能的提升更为显著。最终,对于方法aes_enc_v1进行流水优化后时钟频率达到了127.06 MHz,吞吐量达到了16.26 Gb/s; 对于方法aes_enc_v2进行流水优化后,时钟频率达到121.65 MHz,吞吐量达到了15.57 Gb/s; 而对于方法aes_enc_v3进行流水优化后时钟频率达到了127.06 MHz,吞吐量达到了16.26 Gb/s。因此,可以看出,方法aes_enc_v3在本文所设计方法之中不仅具有最高的性能,而且还具有最优的资源占用。

表 5为与具有代表性的传统硬件设计的横向比较。由于不同的设计基于的FPGA芯片有差异,为公平起见,采用性能面积比 (吞吐率/电路资源数量) 这一指标进行对比。

| 表 5 本文设计与传统设计的比较 Table 5 Comparison of v3_pipeline and traditional hardware designs |

从表 5可以看出,在性能面积比上,本文的设计比之前最好的实验结果提升了44%。因此,本文的设计达到了较好的性能与资源需求之间的平衡,性能面积比是占有优势的。事实上,对于算法的设计要考虑到实际应用的场景,不能一味地追求性能而不考虑到对于资源的需求、器件的成本等因素,需要综合考虑各种因素,从而达到最优的结果。

4 结语在本文的设计中利用高层次综合工具并采用高层次语言 (C语言),描述底层的硬件设计,从而在较高的抽象层面上完成底层设计。在文中不断探讨如何优化C/C++层面的程序设计,并且也讨论了其反映的硬件结构之间的区别。最终,本文完成了一个吞吐量高达16.26 Gb/s、资源需求仅为5 214 Slices的算法设计与实现,与原始的基准设计相比,最终的性能提升了3个数量级。

经过实验表明,利用高层次综合工具完成的设计可以与传统FPGA硬件设计所达到的效果相媲美,而最关键之处在于,本文利用C/C++的高层次综合工具来进行硬件设计的工作效率比传统FPGA硬件设计的工作效率高了许多,而且入门门槛也大大降低。而这也意味着开发人员可以更加专注于应用的功能设计,减少对于底层的关注,并且借助于高层次综合工具探索不同的方法,从而找到最优化的解决方案。

目前对于网络安全性的要求也越来越高,更多的数据流量需要通过加密技术来保证传输。因而,高效、安全、稳定的加密算法的实现研究依旧是一个研究重点,这也是下一阶段研究工作所重点追求的目标。

| [1] | DAEMEN J, RIJMEN V. The Design of Rijndael[M]. New York: Springer-Verlag, 2002 : 31 -50. |

| [2] | 周轶男, 李曦, 冯朝阳. 高速全并行的AES加解密算法在单片FPGA上的实现[J]. 计算机应用, 2004, 24(S2): 102-106. ( ZHOU Y N, LI X, FENG C Y. An implementation of high-speed parallel AES algorithm on a single chip FPGA[J]. Journal of Computer Applications, 2004, 24(S2): 102-106. ) |

| [3] | COUSSY P, TAKACH A. Guest editors' introduction:raising the abstraction level of hardware design[J]. IEEE Design & Test, 2009, 26(4): 4-6. |

| [4] | 党宏社, 王黎, 王晓倩. 基于Vivado HLS的FPGA开发与应用研究[J]. 陕西科技大学学报 (自然科学版), 2015, 33(1): 155-159. ( DANG H S, WANG L, WANG X Q. Development and application of FPGA based on Vivado HLS[J]. Journal of Shaanxi University of Science & Technology (Natural Science Edition), 2015, 33(1): 155-159. ) |

| [5] | MEURER R S, MVCK T R, FROHLICH A A. An implementation of the AES cipher using HLS[C]//Proceedings of the 2013Ⅲ Brazilian Symposium on Computing Systems Engineering. Washington, DC:IEEE Computer Society, 2013:113-118. |

| [6] | 孙桂玲, 纪永鑫, 张潺潺, 等. 基于HLS技术的Rijndael算法IP核实现与优化[J]. 微电子学与计算机, 2010, 27(4): 205-208. ( SUN G L, JI Y X, ZHANG C C, et al. Implementation and optimization of Rijndael arithmetic IP core based on HLS technology[J]. Microelectronics & Computer, 2010, 27(4): 205-208. ) |

| [7] | AHUJA S, GURUMANI S T, SPACKMAN C, et al. Hardware coprocessor synthesis from an ANSI C specification[J]. IEEE Design & Test of Computers, 2009, 26(4): 58-67. |

| [8] | JÄRVINEN K U, TOMMISKA M T, SKYTT J O. A fully pipelined memoryless 17.8 Gbps AES-128 encryptor[C]//Proceedings of the 2003 ACM/SIGDA 11th International Symposium on Field Programmable Gate Arrays. New York:ACM, 2003:207-215. |

| [9] | HUSSAIN U, JAMAL H. An efficient high throughput FPGA implementation of AES for multi-gigabit protocols[C]//Proceedings of the 201210th International Conference on Frontiers of Information Technology. Piscataway, NJ:IEEE, 2012:215-218. |

| [10] | RODRIGUEZ-HENRIQUEZ F, SAQIB N A, DÍAZ-PÉREZ A. 4.2 Gbit/s single-chip FPGA implementation of AES algorithm[J]. Electronics Letters, 2003, 39(15): 1115-1116. doi: 10.1049/el:20030746 |

| [11] | MCLOONE M, MCCANNY J V. High performance single-chip FPGA Rijndael algorithm implementations[C]//Proceedings of the 3rd International Workshop on Cryptographic Hardware and Embedded Systems. London:Springer-Verlag, 2001:65-76. |

| [12] | HENZEN L, FICHTNER W. FPGA parallel-pipelined AES-GCM core for 100 G Ethernet applications[C]//Proceedings of the 2010 European Solid-State Circuits Conference. Piscataway, NJ:IEEE, 2010:202-205. |

| [13] | ZHOU G, MICHALIK H, HINSENKAMP L. Efficient and high-throughput implementations of AES-GCM on FPGAs[C]//Proceedings of the 2007 International Conference on Field-Programmable Technology. Piscataway, NJ:IEEE, 2008:185-192. |

| [14] | ZHOU G, MICHALIK H, HINSENKAMP L. Improving throughput of AES-GCM with pipelined Karatsuba multipliers on FPGAs[C]//Proceedings of the 5th International Workshop on Reconfigurable Computing:Architectures, Tools and Applications. Berlin:Springer-Verlag, 2009:193-203. |

| [15] | LIU Q, XU Z, YUAN Y. A 66.1 Gbps single-pipeline AES on FPGA[C]//Proceedings of the 2013 International Conference on Field-Programmable Technology. Piscataway, NJ:IEEE, 2013:378-381. |

| [16] | PUB N F. Announcing the Advanced Encryption Standard (AES)[S/OL].[2016-05-20]. http://www.just.edu.jo/~tawalbeh/cpe542/slides/aes/fips-197.pdf. |

| [17] | 杨海钢, 孙嘉斌, 王慰. FPGA器件设计技术发展综述[J]. 电子与信息学报, 2010, 32(3): 714-727. ( YANG H G, SUN J B, WANG W. An overview to FPGA device design technologies[J]. Journal of Electronics & Information Technology, 2010, 32(3): 714-727. ) |

| [18] | 田耘, 胡彬, 徐文波. Xilinx ISE Design Suite 10.x FPGA开发指南:逻辑设计篇[M]. 北京: 人民邮电出版社, 2008 : 8 -12. ( TIAN Y, HU B, XU W B. Xilinx ISE Design Suite 10.x FPGA Development Guide:Logic Design[M]. Beijing: Posts and Telecom Press, 2008 : 8 -12. ) |