随着近年来空间探测技术的迅猛发展,星载遥感图像的数据量迅猛提升,受存储空间以及与地面通信传输速度的限制,海量的遥感图像数据已经对星载遥感图像的存储和下行传输造成了巨大的压力,矛盾日益突出, 因此,星载图像压缩技术变得十分重要。

星载遥感图像压缩系统不同于一般的地面图像压缩系统,不仅受限于如体积、功耗等多种特殊因素,对实时性、失真率以及压缩比又有较高的要求。JPEG2000[1]是现今优秀的图像压缩算法, 在遥感数据压缩领域起到了非常重要的作用,且能够提供良好的压缩质量,又具有较高的图像压缩速度,比较适合应用于星载图像压缩系统之中, 硬件方面,常见解决方案有数字信号处理器 (Digital Signal Processor, DSP)、现场可编程门阵列 (Field-Programmable Gate Array, FPGA)、FPGA+DSP[2-3]或FPGA+专用芯片,每种方案都有自己的优势与不足。

DSP已经在星载信号处理系统中得到了广泛的应用, 然而,由于JPEG2000压缩算法相对复杂,采用传统的通用DSP处理器计算性能不强,无法及时处理大量数据,较难达到实时性要求; 采用FPGA加以硬件实现的方式又会导致功耗过大,不能满足功耗上的需求。

现代的新型高性能应用对处理能力和功耗等指标提出了全新的需求,而开发新型的高端DSP所面临的挑战是难以想象的,单纯依靠提升DSP时钟频率会大幅增加功耗,而DSP处理器的典型应用领域通常对功耗非常敏感,需要采用新的架构和理念进行设计。

近年来国内外的研究者提出采用针对运算任务优化的全新架构,通过结构方面的创新来满足日益增长的性能需求。高性能DSP处理器正在向片上多核、可重构阵列处理结构以及流体系结构等方面发展,并结合超长指令字 (Very Long Instruction Word, VLIW)、单指令多数据流 (Single Instruction Multiple Data, SIMD)、专用指令集处理器 (Application Specific Instruction Set Processor, ASIP) 等相关领域的众多新技术。当前国内外成熟的高性能DSP的研究与产品化主要集中在片上多核结构方面,它通过在片上集成多个高性能DSP核来达到提升处理能力的目的。片上多核技术将多个DSP核通过总线集成起来,通过资源复制的方式提供更强大的处理能力。目前TI、Freescale的多款高端DSP芯片即采用这种结构,比如TI的keystone架构的C66x[4-5]系列及Freescale的MSC 81xx系列产品[6]。多核DSP各个核之间的数据交互需通过外围的共享存储器来完成,交互效率较低。考虑到上述因素,多核DSP更适合于粒度较大的线程级并行应用,并且核之间昂贵的同步操作会对系统的性能产生较为严重的影响。

目前新型高性能DSP的商用现成品 (Commercial-Off-The-Shelf, COTS) 器件主要集中在多核DSP上,主要优势在于其拥有多个完整的DSP核,可以同时执行多个完整的任务,更适合于核间通信较少、粒度较大的并行应用,而要发挥多核DSP的优势主要依靠合理地设计软件的架构以减少通信开销并充分利用多核DSP的硬件资源,目前针对多核DSP环境下并行技术的研究尚不深入。

1 C66x架构分析 1.1 C66x多核DSP介绍C66x系列处理器是TI公司的多核DSP系列处理器,拥有良好的性能与丰富的功能。

1) 每DSP内核高达1.25 GHz定点和浮点性能; 2) 单核至八核可扩展性; 3) 采用KeyStone架构提高多核性能; 4) 大型嵌入式存储器和高带宽DDR3/DDR3L接口; 5) 网络协处理器 (NetCP) 选项,包括安全性和数据包加速; 6) 高速IO,包括PCIe、串行RapidIO、千兆位以太网、超链接全新的C66x定点/浮点内核单个器件上可实现最高320 GMAC (Giga Multiply-ACcumulate operation, 每秒10亿次乘法累积操作) 和160 GFLOP (Giga Floating-point Operations Per Second, 每秒10亿次浮点运算数) 定点及浮点整合性能[7],整合多个DSP,节省板级空间,降低成本和电源需求。

DSP内部的层级存储器,可根据应用具体需求进行配置,具有较高的灵活性。

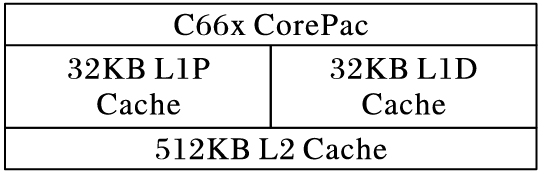

1.2 C66x CorePac概述图 1为C66x CorePac部分[8-9],为C66x的核芯,不同型号C66x DSP拥有不同数量CorePac。每个CorePac内部包含以下层级存储器。

|

图 1 C66x CorePac Figure 1 C66x CorePac |

32 KB L1D (Level 1 Data) 静态随机存取存储器 (Static Random Access Memory,SRAM),它和DSP核运行在相同的速度上,可以被用作普通的数据存储器或数据Cache,Cache大小可以在4 KB、8 KB、16 KB、32 KB之间任意选择配置。

32 KB L1P (Level 1 Program) SRAM,它和DSP核运行在相同的速度上,可以被用作普通的程序存储器或程序Cache,Cache大小可以在4 KB、8 KB、16 KB、32 KB之间任意选择配置。

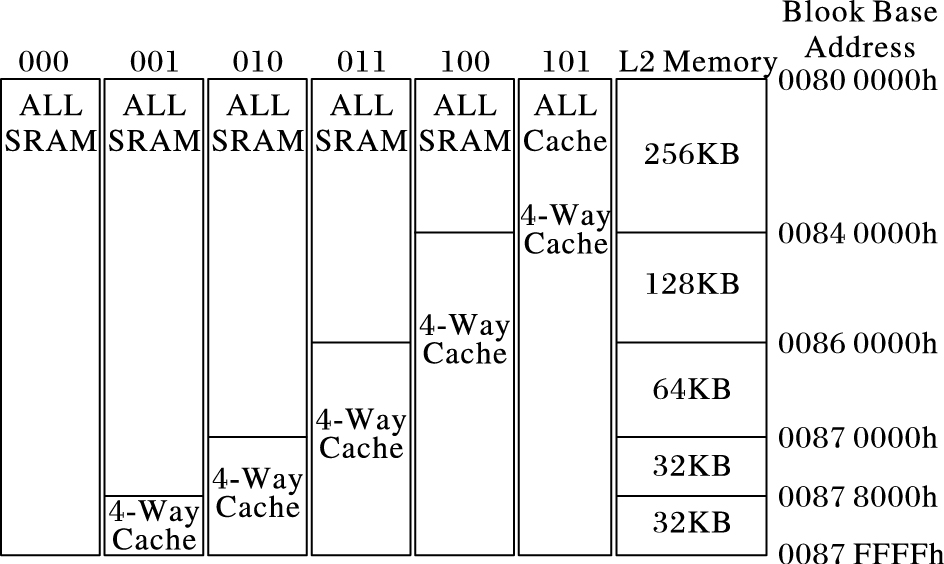

512 KB LL2 (Local Level 2) SRAM,它的运行速度是DSP核的一半,可以被用作普通存储器或Cache,既可以存放数据也可以存放程序,Cache大小可以在32 KB、64 KB、128 KB、256 KB、512 KB之间任意选择配置 (图 2)。

|

图 2 L2配置策略 Figure 2 L2 configuration |

面向星载的多核DSP并行图像压缩系统设计,需要设计者根据星载的要求,并结合多核DSP硬件的自身特点对原有串行程序进行并行化改造移植,需要系统尽量简洁、可靠,留下可扩展空间,同时充分利用硬件性能,提升运行效率。本章基于TI的C6678硬件平台设计了多核DSP上的并行图像压缩系统。

2.1 系统应用场景作为星载设备的一部分,系统通过PCI-E (Peripheral Component Interconnect-Express) 与主控端进行连接,接受主控端 (Host) 按幅传入的带编号记录的RAW格式原始图像,像素为4 096×2 048,每个像素点占用2 B数据,每幅原始图像大小为16 MB,经系统压缩后传回压缩结果数据至主控端并告知对应图像编号,主控端将压缩结果传回地面机进行下一步处理。整个系统需要尽可能提升整体压缩性能,提高系统的整体吞吐量。

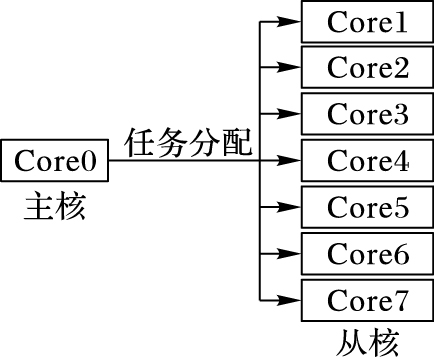

2.2 并行系统设计C6678多核DSP拥有8个C66x核心Core0~Core7,每个核心都可以相对独立完成常规单核DSP可以完成的任务,其中Core0可以实现与其他外设、接口的通信功能,功能上Core0与其他7个核并不对称,因此整个系统的并行模型采用如图 3的主从模型 (Master/Slave Model),Core0作为主核,Core1~Core7作为从核。系统还设计了0、1号2个16 MB的PCI-E输入缓冲区,1个4 MB的PCI-E输出缓冲区,1~16号16个20 MB图像缓冲区,其中每个图像缓冲区分为16 MB的图像输入缓冲区与4 MB的图像输出缓冲区两个部分。

|

图 3 主从模型 Figure 3 Master/Slave model |

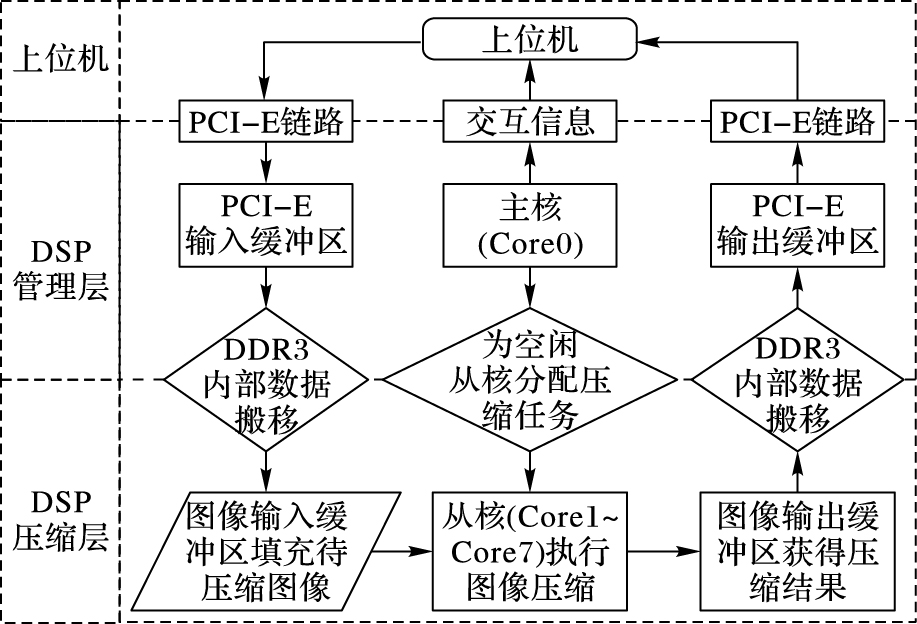

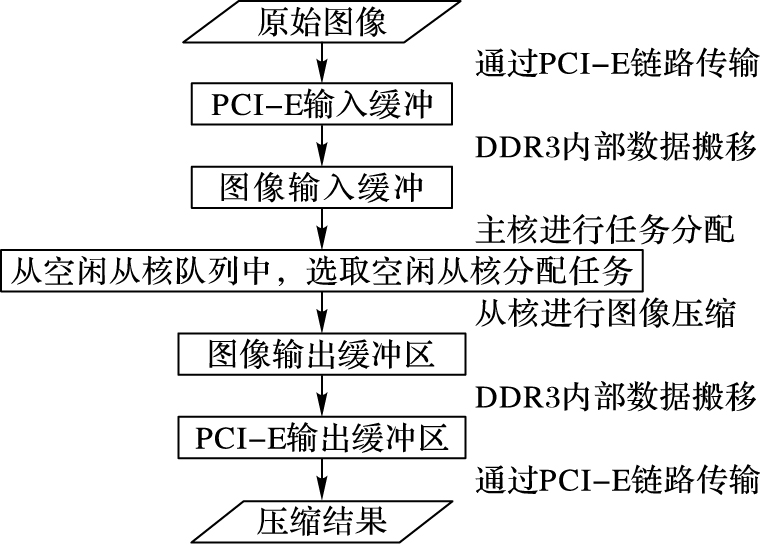

如图 4的系统架构所示,Core0作为主核对外与上位机进行通信,利用PCI-E输入缓冲区获取原始图像数据,通过PCI-E输出缓冲区向主控端传回压缩结果;对内Core0将从PCI-E输入缓冲区获取的原始图像数据填入16个图像输入缓冲区,并将已有原始图像数据的图像缓冲区作为一个任务,分配给空闲的从核,Core1~Core7没有压缩任务时将一直空闲等待,接收到Core0的任务后将处理相应地图像缓冲区的图像输入缓冲区部分,并将压缩结果存入对应图像缓冲区的图像输出缓冲区部分,压缩完成后Core1~Core7告知Core0当前缓冲区任务处理完毕,进入空闲等待状态,等待下一轮任务;Core0接到从核压缩任务完成通知后,将对应图像输出缓冲区的压缩结果搬运到PCI-E图像输出缓冲区,并与主控端通信,等待主控端通过PCI-E链路取回压缩结果,系统的图像压缩流程如图 5。

|

图 4 压缩系统架构 Figure 4 Architecture of compression system |

|

图 5 图像压缩流程 Figure 5 Image compression process |

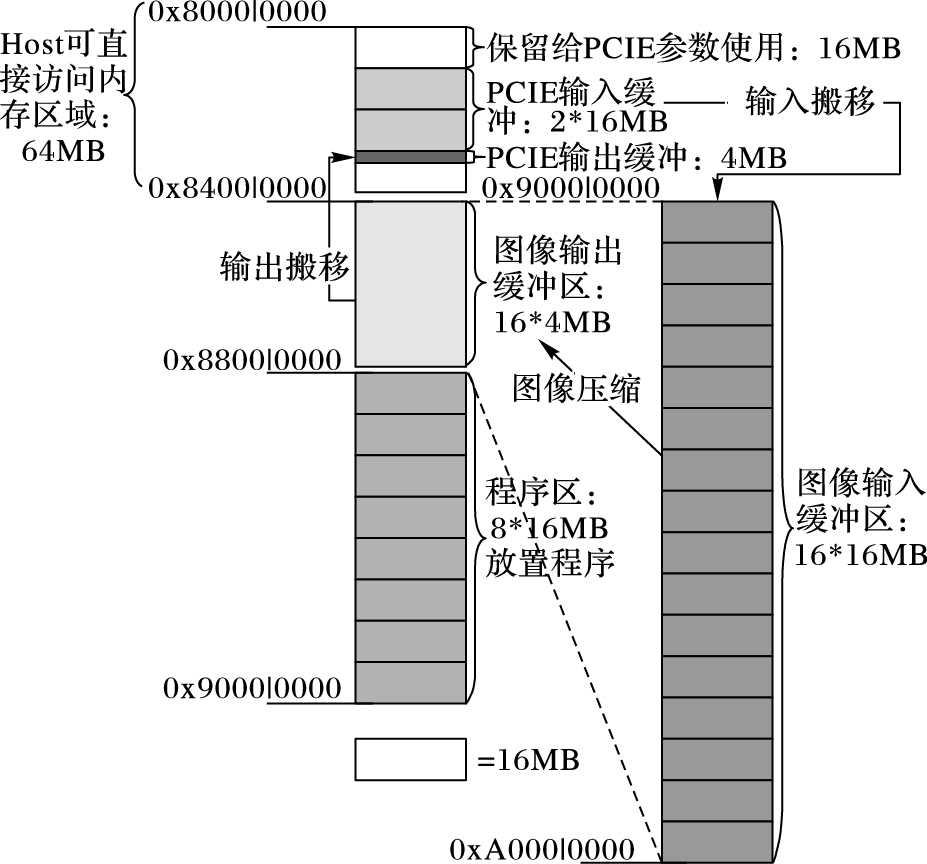

C6678允许用户自由配置每个层级的存储器,该系统中,C6678的每个C66x核心拥有的32 KB L1D与32 KB L1P以及512 KB L2,C6678最大支持从全局地址0x80000000开始的最大2 GB DDR3内存,本系统使用的C6678硬件平台配有512 MB DDR3内存,地址为0x80000000~0x9FFFFFFF, 具体DDR3的规划见图 6与表 1。

|

图 6 DDR3内存规划 Figure 6 DDR3 memory planning |

| 表 1 DDR3存储规划 Table 1 DDR3 storage planning |

考虑到DDR3速度较低,因此为避免从核处理完一个压缩图像任务后因为等待图像缓冲区填充新的原始图像数据而长时间进入进入空闲等待状态而影响性能,系统为此设计了超过7个从核两倍数量的16个图像缓冲区,从核完成一个压缩任务后可以立刻分配到新的任务,避免因为等待数据输入引起的性能损失。

3.2 DDR3内部数据搬移系统中存在两个数据搬移过程:1) 将原始图像由PCI-E缓冲区搬移至图像输入缓冲区;2) 将图像压缩结果由图像输出缓冲区搬移至PCI-E输出缓冲区。若由Core0直接进行数据搬移,由数据搬移期间Core0无法进行其他操作,且该过程将占用大量时钟周期,会直接影响Core0对Core1~Core7的任务分配效率,也会影响Core0与主控端通信的效率。因此,有必要采用直接内存访问 (Direct Memory Access, DMA) 的形式进行数据搬移。

增强型直接内存访问 (Enhanced Direct Memory Access, EDMA) 是DSP中一种高效的数据传输模块,能够不依赖CPU进行数据的搬移,是在高速接口的使用中十分重要的设备。与EDMA模块相比,EDMA3在传输的同步方式、地址跳变、触发方式上都变得更为灵活。表 2为C6678工作在1 GHz频率下,DSP核与EDMA3进行DDR3内部数据搬移的实际测试性能,可以看出,EDMA3的实际速度约为DSP核的两倍,采用EDMA3进行数据搬移可以极大提高数据搬移效率,释放DSP核性能,消除潜在性能瓶颈。

| 表 2 DDR3内部数据搬移速度结果 MB/s Table 2 DDR3 internal data movement speed MB/s |

由于JPEG2000算法较为复杂,其中小波与EBC (Embedded Block Coding) 编码部分需要用到大量运行空间,所以实际运行时占用空间较大 (约为15.5 MB),因此每个核的程序部分都分配有16 MB DDR3空间,其中包括代码段、堆栈段、数据段、系统数据段等部分,原有分配策略为程序所有段全部置于16 MB的DDR3空间中,L2全部配置成512 KB Cache。由于DDR3相较L2速度较慢,可以将L2配置为Cache+SRAM的模式,并将部分程序段直接转移至L2中,以进一步提高程序运行速度。

通过分析CCS (Code Composer Studio) 编译记录文件可以获知程序各段大小,结合不同L2配置策略将比较小的段置于L2中并进行实验,通过实验决定最终配置方案。

4 并行图像压缩系统性能验证及分析 4.1 实验环境本文所设计并行图像系统使用C++语言在TI提供的IDE CCS中编译实现,硬件为星载项目现有C6678(8核) 开发平台,用于对C6678多核处理器调试的Blackhawk XDS560v2高性能TI处理器系统跟踪USB仿真器。实验采用真实遥感图像数据,格式为RAW,分辨率4 096×2 048,每个像素点2B数据,与实际星载应用一致。

4.2 程序段位置与L2配置实验实验方式为C6678单核模式下压缩400幅图像数据,统计不同配置下的运行时间,计算出每种配置下的每秒压缩速度。

表 3为CCS编译记录文件提供的各主要程序段大小数据,由于L2只有512 KB空间,因此表 4中除.far与.sysmen程序段外小于512 KB的程序段都可以参与实验。

| 表 3 程序段大小 Table 3 Program block size |

| 表 4 程序段位置及L2配置测试结果 Table 4 Test results of block location and L2 configuration |

实验分为512 KB L2 Cache;256 KB L2 Cache,程序段全部设置于DDR3中;256 KB L2 Cache,程序段部分设置于L2 SRAM中;128 KB L2 Cache,程序段全部设置于DDR3中;128 KB L2 Cache,程序段部分设置于L2 SRAM中共5种类情况,并加入L2 Cache为64 KB、32 KB、0 KB时的实验结果作为对比。实验结果见表 4。

实验结果显示,在L2 Cache大小为512 KB与256 KB时,压缩速度一样,说明L2 Cache大小完全满足程序需求,当L2 Cache大小降低到128 KB及以下时压缩性能开始加速下降;将程序段大小小于L2 SRAM的部分由DDR3移入L2中可以提升压缩速度,但是效果不明显。结合实验结果,设置L2 Cache 256 KB, 除.far与.sysmen外程序段全部设置在L2 SRAM中,可以获得一个最优的单核图像压缩性能。

4.3 系统性能验证实验实验环境中的硬件与软件条件与4.1节完全相同,按照4.2节结论配置L2与程序段位置。实验方式为统计单核下与多核下各自压缩400幅大小图像数据所用时间,多核下以最后一个完成压缩任务的时间为准,计算出每秒压缩速度为系统的性能 (表 5)。

| 表 5 图像压缩性能测试实验结果 Table 5 Performance test results of image compression |

核数 P=8;加速比S=T1/T8=6.96;效率E=S/P=0.87, 效率E=0.87近似等于7/8,其中T1表示单核运行时间,T8表示8核运行时间。考虑到主核不进行图像压缩,只有7个从核执行图像压缩程序,说明进行图像压缩的7个从核的压缩性能和单核状态一样,并没有因为共享DDR3而碰到性能瓶颈,整个系统也没有因为PCI-E缓冲区与图像缓冲需要进行数据搬移而影响性能。

5 结语本文基于多核DSP架构特点设计了一个并行面向星载遥感图像压缩系统, 分别针对并行模型与存储区域规划进行研究,设计并实现了完整的系统。实验结果表明整个系统运行稳定可靠,在8核DSP上获得了相对单核DSP 7倍的较好的加速比。针对星载应用领域的特点,后续工作将在系统的可靠性方面展开进一步的研究。

| [1] | 刘方敏, 吴永辉. JPEG2000图像压缩过程及原理概述[J]. 计算机辅助设计与图形学学报, 2002, 14(10): 905-911. ( LIU F M, WU Y H. Image compression process and principle of JPEG2000[J]. Journal of Computer Aided Design & Computer Graphics, 2002, 14(10): 905-911. doi: 10.3321/j.issn:1003-9775.2002.10.002 ) |

| [2] | 马瑞敏, 王景宇, 王国权. 空间太阳望远镜FPGA星载图像压缩模块的设计与实现[J]. 宇航学报, 2008, 29(4): 1345-1349. ( MA R M, WANG J Y, WANG G Q. The development and implementation of FPGA compressed module for onboard images of space solar telescope[J]. Journal of Astronautics, 2008, 29(4): 1345-1349. ) |

| [3] | 朱火龙. 基于多核DSP的弹载SAR成像信号处理系统设计[D]. 西安: 西安电子科技大学, 2014. ( ZHU H L. Signal processing system design of missile-borne SAR imaging based on multicore DSP[D]. Xi'an:Xidian University, 2014. ) |

| [4] | Instruments T. TMS320C66X DSP CorePac user guide[EB/OL].[2016-06-20].http://www.ti.com/lit/ug/sprugw0b/sprugw0b. |

| [5] | Incorporation T I. TMS320C66x DSP CPU and instruction set reference guide[EB/OL].[2016-06-20]. http://www.docin.com/p-406159018.html. |

| [6] | 绳伟光, 蒋剑飞, 何卫锋. 高性能DSP的发展现状与未来趋势[J]. 中国集成电路, 2011, 20(4): 20-25. ( SHEN W G, JIAN J F, HE W F. State of the art and future trends of high performance DSPs[J]. China Integrated Circuit, 2011, 20(4): 20-25. ) |

| [7] | Instruments T. TMS320c6678 Multicore fixed and floating-point digital signal processor[EB/OL].[2016-06-20].http://www.ti.com/lit/ds/symlink/tms320c6678.pdf. |

| [8] | 郝朋朋, 周煦林, 唐艺菁, 等. 基于TMS320C6678多核处理器体系结构的研究[J]. 微电子学与计算机, 2012, 29(12): 171-175. ( HAO P P, ZHOU X L, TANG Y J, et al. Research on multicore processor's architecture based on TMS320C6678[J]. Microelectronics & Computer, 2012, 29(12): 171-175. ) |

| [9] | 牛金海. TMS320C66x KeyStone架构多核DSP入门与实例精解[M]. 上海: 上海交通大学出版社, 2014 : 137 -275. ( NIU J H. TMS320C66x Keystone Architecture Getting Started with Multicore DSP and Example Solution[M]. Shanghai: Shanghai Jiaotong University Press, 2014 : 137 -275. ) |

| [10] | Texas Instruments. KeyStone architecture multicore navigator user guide[EB/OL].[2016-06-20]. http://www.ti.com/lit/ug/sprugr9h/sprugr9h.pdf. |

| [11] | Texas Instruments. Multicore programming guide[EB/OL].[2016-06-20]. https://www.mendeley.com/research/multicore-programming-guide. |

| [12] | MUKHERJEE S S, KONTZ M, REINHARDT S K. Detailed design and evaluation of redundant multi-threading alternatives[C]//Proceedings of the 29th Annual International Symposium on Computer Architecture. Piscataway, NJ:IEEE, 2002:99-110. |

| [13] | TULLSEN D M, EGGERS S J, LEVY H M. Simultaneous multithreading:maximizing on-chip parallelism[J]. ACM SIGARCH Computer Architecture News, 1995, 23(2): 392-403. doi: 10.1145/225830 |

| [14] | 孙科林, 周维超, 吴钦章, 等. 光纤实时传输的多核DSP图像处理系统[J]. 光电工程, 2012, 39(4): 136-144. ( SUN K L, ZHOU W C, WU Q Z, et al. A multi-core DSP image processing system based on optical fiber transmission real-time[J]. Opto-Electronic Engineering, 2012, 39(4): 136-144. ) |

| [15] | LAFRIEDA C, IPEK E, MARTINEZ J F, et al. Utilizing dynamically coupled cores to form a resilient chip multiprocessor[C]//Proceedings of the 37th Annual IEEE/IFIP International Conference on Dependable Systems and Networks. Piscataway, NJ:IEEE, 2007:317-326. |

| [16] | Texas Instruments. KeyStone Enhanced Direct Memory Access (EDMA3) controller user guide[EB/OL].[2016-06-20].http://www.ti.com.cn/cn/lit/ug/sprugs5a/sprugs5a.pdf. |

| [17] | 周佩, 周维超, 王凯凯. TMS320C 6678多核DSP并行访问存储器性能的研究[J]. 微型机与应用, 2014, 33(13): 20-24. ( ZHOU P, ZHOU W C, WANG K K. Research on performance of TMS320C 6678 multicore DSP parallel memory access[J]. Microcomputer & its Applications, 2014, 33(13): 20-24. doi: 10.3969/j.issn.1674-7720.2014.13.007 ) |

| [18] | 潘晔, 廖昌俊. TI-DSP多核技术及实时软件开发[M]. 北京: 电子工业出版社, 2016 : 242 . ( PAN Y, LIAO C J. TI-DSP Multi-core Technology and Real-time Software Development[M]. Beijing: Publishing House of Electronics Industry, 2016 : 242 . ) |

| [19] | 牛金海. TI C66x多核软件开发 (MCSDK) 技术[M]. 上海: 上海交通大学出版社, 2015 : 286 -341. ( NIU J H. TI C66X Multi-Core Software Development (MCSDK) Technology[M]. Shanghai: Shanghai Jiaotong University Press, 2015 : 286 -341. ) |

| [20] | PACHECO P S. 并行程序设计导论[M]. 邓倩妮, 等译. 北京: 机械工业出版社, 2013: 151-271. ( PACHECO P S. An Introduction to Parallel Programming[M]. DENG Q N, et al., translted. Beijing:China Machine Press, 2013:151-271. ) |

| [21] | 周伟明. 多核计算与程序设计[M]. 武汉: 华中科技大学出版社, 2009 : 13 -549. ( ZHOU W M. Multi-core Computing and Programming[M]. Wuhan: Huazhong University of Science and Technology Press, 2009 : 13 -549. ) |

| [22] | 苏保禹. 基于TI-C6678的多核DSP图像处理系统研究[D]. 北京: 中国科学院大学, 2014. ( SU B Y. Research on multi-core DSP image processing system based on TI-C6678[D]. Beijing:University of Chinese Academy of Sciences, 2014. ) |