2. 高性能计算国家重点实验室 (国防科学技术大学), 长沙 410073

2. State Key Laboratory of High Performance Computing (National University of Defense Technology), Changsha Hunan 410073, China

当前,信息技术高速发展,大数据时代到来,存储系统规模变得日益庞大,信息的存储和处理面临着巨大的挑战[1]。为满足数据密集型计算日益增长的性能需求,存储设备经历了多次技术革新,基于闪存 (Nand Flash) 的固态盘 (Solid-State Driver, SSD) 凭借低延时、低功耗、高带宽和高并行性等方面的技术优势,赢得了云计算、高性能计算等领域的青睐[2],并带动了消费级存储市场的发展。据国际市场研究者IHS公司预测,到2017年,固态盘将占整个计算机存储市场的33%以上[3]。

固态盘接口是固态盘与主机系统进行数据交互的通路,决定了二者之间进行数据传输的方式,限制了主机与固态盘的峰值传输速度。随着闪存技术的不断进步、存储系统性能要求的提高,传统上基于SATA (Serial ATA)/SAS (Serial Attached SCSI) 的固态硬盘已经不能满足需求,采用PCIE (Peripheral Component Interconnect Express) 接口的固态硬盘依然需要经过外设存储协议层,存在访存路径过长的问题,在性能要求苛刻的场合还是无法满足需求。采用DDR3(Double-Data-Rate Three synchronous dynamic random access memory) 接口设计SSD具有访存路径短、带宽大、低延迟等特点[4],可充分发掘固态盘内部的并行性,提高固态盘整体性能。

依据接口性能,可将SSD划分为3代。第1代SSD采用SATA/SAS接口进行数据传输,带宽有限,其中面向消费级市场采用的SATA Ⅱ、SATA Ⅲ接口带宽分别为300 MB/s和600 MB/s[5], 而面向企业级市场采用的SAS接口带宽则达到600 MB/s[6]。随着SSD技术的进步以及市场发展的需求,人们基于PCIE接口设计了第2代SSD, 旁路掉传统SATA/SAS数据通路中的HBA (Host Bus Adapter),访存延时获得了一个数量级的提升。虽然PCIE SSD性能具有优势,然而由于PCIE总线访存路径的限制,其读写响应时间依然比较长,达到40~70 ms;另一方面,PCIE总线上需要挂载大量的各种设备,导致总线竞争激烈,以至于PCIE SSD的I/O性能无法得到线性的扩展[7]。为减小SSD的存取路径长度,降低读写数据延时,提高I/O可扩展性能,人们提出了采用DDR3接口设计的第3代SSD存储产品。

基于DDR3接口的第3代SSD在位置上更加靠近CPU,并直接与CPU相连,旁路掉所有外设的存储协议层,因此能够获得超低的访问延时 (ultra-low latency)。该SSD存储设备通过内存总线 (memory bus) 进行数据传输,遵从DDR3总线协议,采用同步数据传输方式与CPU进行数据交互,相对于PCIE SSD采用的异步传输方式更加高效。在企业级的高性能、大数据处理方面,尤其是对于存储设备延迟有着苛刻要求的应用场合上,它能够较好地满足性能方面的要求,因此可广泛应用于高频交易、大数据分析、虚拟桌面基础架构、内存计算、刀片服务器等领域[8]。

本文的研究工作是针对DDR3接口信号,严格按照JEDEC (Joint Electron Device Engineering Council) 规定的时序进行协议解析与控制,包括命令解析、地址译码、数据格式转换、接口I/O同步控制等,将DDR3接口信号转换成SSD后端可识别的信号,并完成接口同步数据传输与交互。

本文实验基于FPGA (Field-Programmable Gate Array) 可编程逻辑器件,采用Verilog硬件描述语言设计解析逻辑。实验中搭建完整的硬件仿真平台,通过Xilinx ISE软件生成的MIG (Memory Interface Generator) 核作为内存控制器,以产生内存控制信号。解析逻辑按照内存时序规范对接口信号进行解析与控制,完成数据的接收与发送、执行对后端FTL (Flash Translation Layer) 发送过来的请求进行处理等工作。实验最后对解析逻辑进行了完整的测试和验证,并对实验结果进行了分析。

1 DDR3工作原理及协议解析设计难点 1.1 DDR3工作原理DDR SDRAM (Double-Data-Rate SDRAM) 即双倍速率同步动态随机存储器,由SDRAM (Synchronous Dynamic Random Access Memory) 基础上发展而来,采用时钟的上升沿和下降沿均进行数据采样,从而把数据传输速率提高了一倍[9]。DDR内存技术已经历四代的发展,每一代内存芯片的核心频率都维持在100~200 MHz,但在I/O性能上都有大幅度提升。这种性能提升一方面得益于半导体晶圆制造工艺的发展,另一方面是因为采用了双倍数据速率传输 (Double Data Rate) 和预取 (prefetch) 两项核心技术[10]。

DDR3是第3代双倍速率同步动态随机存储器。采用8 b预取技术,管脚时钟频率由之前内核频率的2倍提升到4倍,到达800 MT/s~1 600 MT/s。

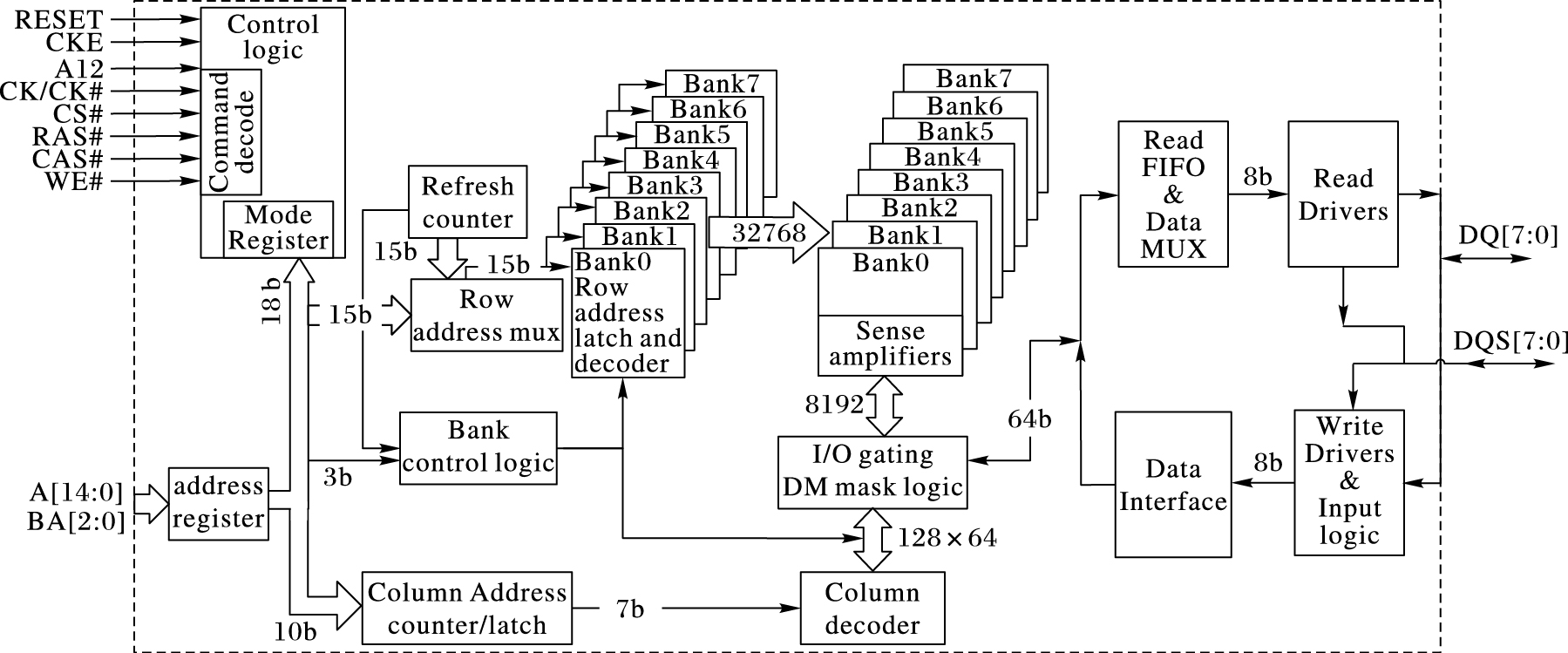

DDR3内存主要由内存芯片和基板构成。内存芯片是数据存储区,内存基板将8颗或16颗内存芯片整合在一块PCB板上构成一根内存条。内存芯片如图 1所示,左边是存储阵列和访存控制逻辑 (Control Logic),右边是数据缓存区。存储阵列在逻辑上被划分为8个Bank,每个Bank都有独立的行列地址译码逻辑。进行数据读/写操作时,控制逻辑通过对命令信号的译码,识别访存指令,从而控制地址功能部件定位存储阵列访存位置。缓存逻辑部分负责读写数据的缓冲,读操作时,将预取的64 b数据送入读数据缓冲区 (Read FIFO),然后分成8路,通过数据多路复用器 (Data MUX) 合并成一路数据流输出到接口。写缓冲是读缓冲的逆过程。

|

图 1 256 MB ×8的DDR3芯片功能框图 Figure 1 Functional block diagram of DDR3 chip with 8 banks of 256 MB |

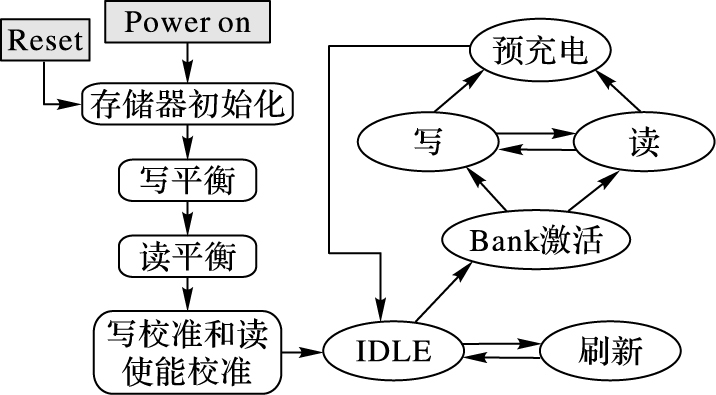

DDR3整体上的基本工作流程如图 2所示。上电之后重置,对其每一颗芯片内部的控制逻辑及存储单元进行初始化,然后设置模式寄存器 (Mode Register) MR2、MR3、MR1、MR0,完成一系列的读写校准操作,才正式进入工作模式。正常工作模式下的操作包括激活 (Bank Active)、读 (Read)、写 (Write)、刷新 (Refresh)、预充电 (Precharge) 及低功耗模式下的相关操作,所有操作都须严格按照JEDEC规范[10]的时序要求进行。

|

图 2 DDR3 SDRAM操作流程 Figure 2 DDR3 SDRAM operation state diagram |

DDR3接口的访存信号由内存控制器向DDR3发出,通过内存总线传送到DDR3接口。本文依据JEDEC标准对内存总线信号进行解析。本文采用Xilinx公司的ISE软件生成的MIG核作为DDR3内存控制器,以生成DDR3接口访存信号源。

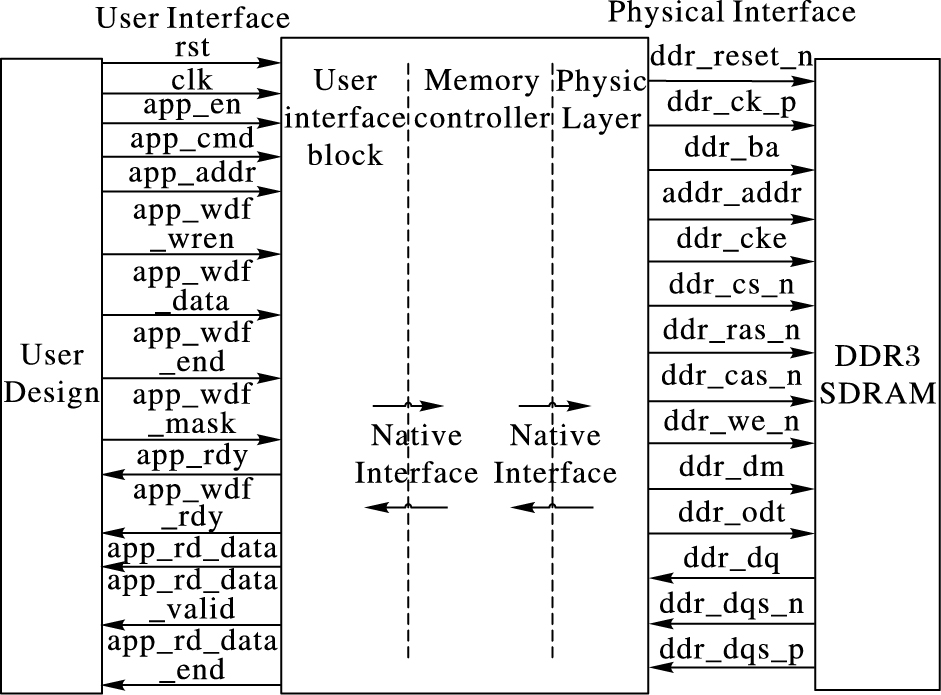

基于Virtex-6 FPGA的内存控制器逻辑如图 3所示。中间部分是内存控制器,两边的是用户接口 (User Interface, UI) 信号和DDR3内存访问信号。用户逻辑模拟CPU的访存行为,向内存控制器发出读/写访存命令,并通过用户接口送达内存控制器。DDR3内存访问信号则具体用于对DDR3存储器进行访存。

|

图 3 Virtex-6 FPGA存储器接口逻辑框图 Figure 3 Logical diagram of Virtex-6 FPGA memory interface |

本文设计DDR3协议解析逻辑通过图 3右边的DDR3接口信号完成与内存控制器之间的交互。实验最终在左端User Design部分设计读写测试激励,验证解析逻辑的正确性并测试读写性能。

1.3 DDR3协议解析设计难点根据JEDEC标准 (JESD79-3) [11]规定的DDR3内存总线时序规范,对协议进行研究与分析,本文设计DDR3协议解析逻辑有以下难点:

1) DDR3 SDRAM在进行正式的读写操作之前需要完成漫长的初始化、校准操作,直至控制器置信号phy_init_done有效,用户逻辑才能通过控制器进行读写操作。因此,在初始化及校准操作完成之前,解析逻辑只能被动地配合控制器进行数据交互。只有完成初始化及校准流程才能验证前期工作的正确性,而无法一步一步迭代前进,这为解析逻辑的设计带来了不小的挑战。

2) DDR3总线协议采用同步时序控制方式,在进行读写访问时,从Bank激活到读/写命令发出,再到数据送达总线,每一步都有固定的延时限制,延时长度由相关参数设定。在与激活操作相对固定的时间点上必须完成相关数据操作, 否则会造成读写数据出错。延时精确控制是解析逻辑设计中有待重点解决的问题。

3) DDR3接口信号采用双边沿触发数据采样机制,采样时钟为数据的源同步信号DQS,频率与时钟相同。基于FPGA设计解析逻辑,在400 MHz的工作时钟下,如何完成双边沿触发数据采样,并且保证采样的准确性,是研究中的难点。

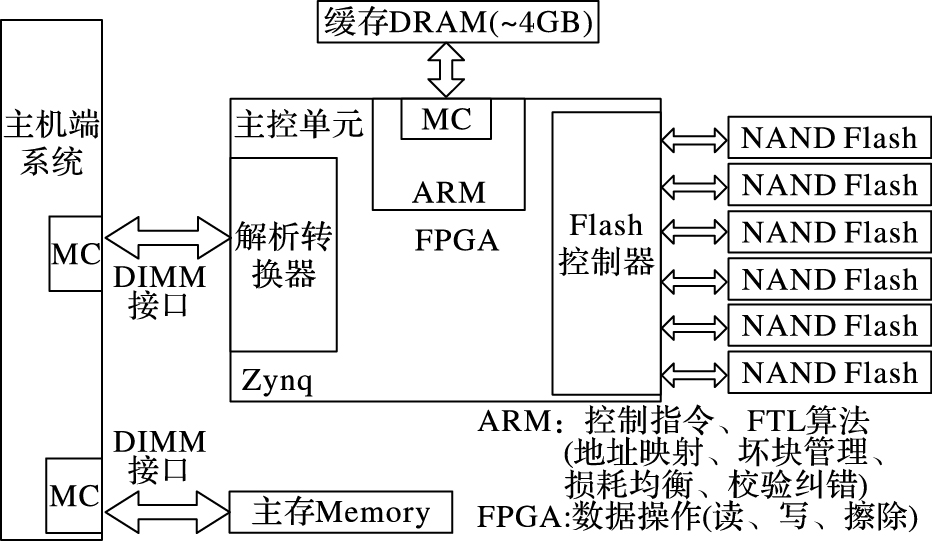

2 解析逻辑设计方案 2.1 基于DDR3接口的固态盘架构基于DDR3接口的SSD原型系统是课题组正在研发的一款大容量、高性能的固态存储系统,主要针对企业级高性能计算、大数据处理等对访存延时要求苛刻的领域。原型系统采用较为成熟的系统架构方案,由主控制器、DRAM缓存和Flash存储空间三部分构成。主控制器采用FPGA可编程逻辑+ARM核实现,用于对存储系统的读写控制和访存调度,是原型系统的核心;DRAM缓存采用大容量的DDR3芯片,集成在固态盘内部,用于缓冲Flash中的热点数据,以提高固态盘的读写性能;Flash存储空间由多颗NAND Flash构成,形成大容量的数据存储区。基于DDR3接口的固态盘原型系统总体架构如图 4所示。

|

图 4 基于DDR3接口的固态盘原型系统架构 Figure 4 Architecture of SSD prototype based on DDR3 interface |

固态盘主控制器是实现高性能数据读写的关键。本课题研制的基于DDR3接口的固态盘原型系统采用带有ARM核的Zynq芯片作为主控单元。Zynq中集成了ARM核和FPGA可编程逻辑,主控制器使用ARM核作为指令控制单元,以实现FTL算法;使用FPGA,利用硬件的并行处理特性实现高效数据传输与控制等。

原型系统通过DIMM (Dual-Inline-Memory-Modules) 插槽直接与主机相连,主机CPU通过内存控制器 (Memory Control, MC) 像访问内存一样访问该固态存储设备。图 4中解析转换器即为本文所要实现的协议解析逻辑模块,涉及与两端的通信,一端是对DIMM接口信号进行解析,另一端是与主控制器后端控制逻辑进行交互。本文主要完成针对与DIMM接口信号进行交互的设计工作。

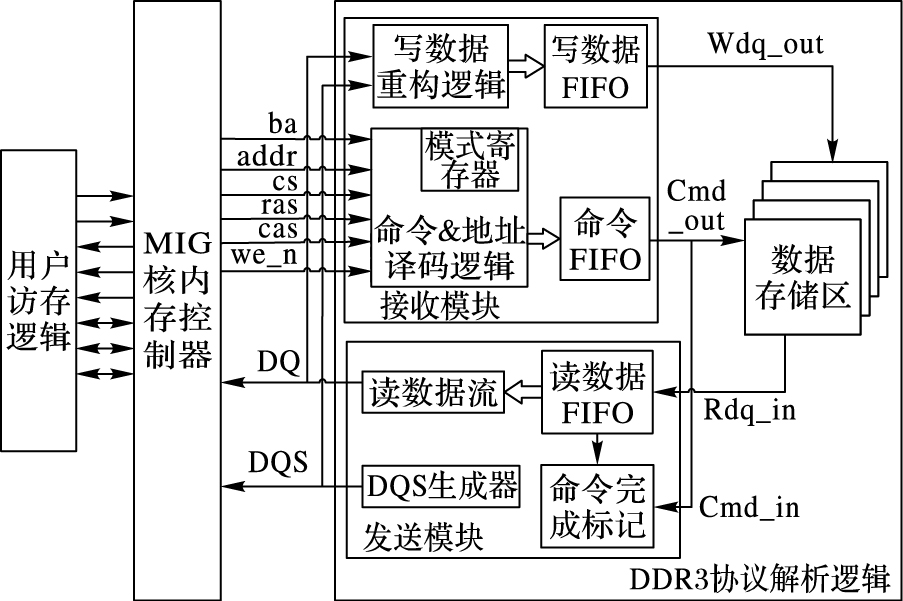

2.2 DDR3协议解析逻辑设计DDR3协议解析逻辑作为固态盘与主机CPU进行交互的桥梁和纽带,是整个固态盘系统中非常重要的一环,其设计方案如图 5所示。其中包括三部分:用户访存逻辑、MIG核实现的内存控制器以及DDR3协议解析逻辑,整个解析逻辑架构都在FPGA上实现和验证。

|

图 5 固态盘解析逻辑的整体结构 Figure 5 Overall structure of SSD parsing logic |

待解析的DDR3接口信号主要有三类:地址、命令和数据信号,根据这些信号状态,解析逻辑完成相应的数据收发功能。图 5右侧是协议解析逻辑,主要包括接收模块、发送模块和数据存储区三个部分。接收模块用于接收MC发送的指令和数据,并进行重构与缓存;发送模块则将读出的数据缓存,并以数据流的方式发送出去;存储数据区用来保存数据。由于解析转换器没有与主控单元后端相衔接,因此这里将后端部分用一个数据存储区表示,以完成对DDR3接口信号的解析功能,并保证读写时序的正确性。

解析逻辑中接收模块包含写数据重构逻辑和命令 & 地址译码逻辑及两个FIFO (First Input First Output) 缓冲区。写数据重构逻辑在特定的时刻对有效数据进行采样并缓冲到写数据FIFO中。命令&地址译码逻辑则根据命令信号cs_n、ras_n、cas_n、we_n的高低电平组合译码成DDR3操作指令,如表 1所示 (H表示高电平,L表示低电平);根据地址信号ba、addr及命令信号进行行列地址识别;在初始化阶段,模式寄存器会根据地址和命令信号进行相应的参数设置。

| 表 1 DDR3命令真值表 Table 1 DDR3 command truth value table |

协议解析逻辑中的发送模块将从数据存储区中读回的数据缓存入读数据FIFO中并在特定的时刻以数据流的形式连续发送到DDR3接口,输出数据; 同时,双向数据选通 (Data Strobe Signal, DQS) 生成器会产生数据选通信号DQS,与有效数据信号同步输出。本文设计的DDR3协议解析逻辑采用可综合的Verilog硬件描述语言实现,综合出的比特流文件打入FPGA中验证,完成设计与实现工作。

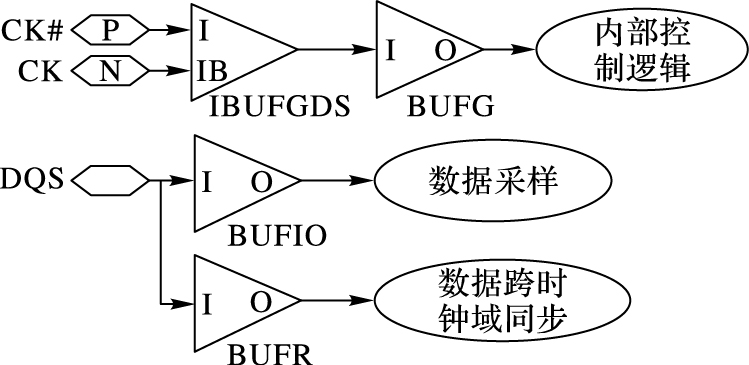

3 DDR3协议解析逻辑实现 3.1 时钟网络在基于FPGA的数字电路设计中,时钟是设计中非常关键的环节,合理地利用各种时钟资源设计时钟网络,可有效改善所设计的FPGA数字逻辑电路的综合和实现效果。本文设计的协议解析逻辑时钟资源主要分为两种:系统工作时钟和源同步时钟。其中,系统工作时钟由MC通过接口时钟管脚CK/CK#输入,驱动解析逻辑大部分工作,包括译码、控制、数据存储和DQS信号生成等;源同步时钟即数据选通信号DQS, 在读写操作时与数据信号DQ (Data Strobe) 同步传输,并使用它对DQ信号进行精确采样和提取,获取有效数据。

文中内存控制器采用DDR3-800的内存条参数,因此解析逻辑的系统工作时钟为400 MHz, 符合Xilinx FPGA所限制的时钟频率范围,而源同步时钟DQS只有在接口进行数据传输时才有效,频率上与系统工作时钟CK相同。

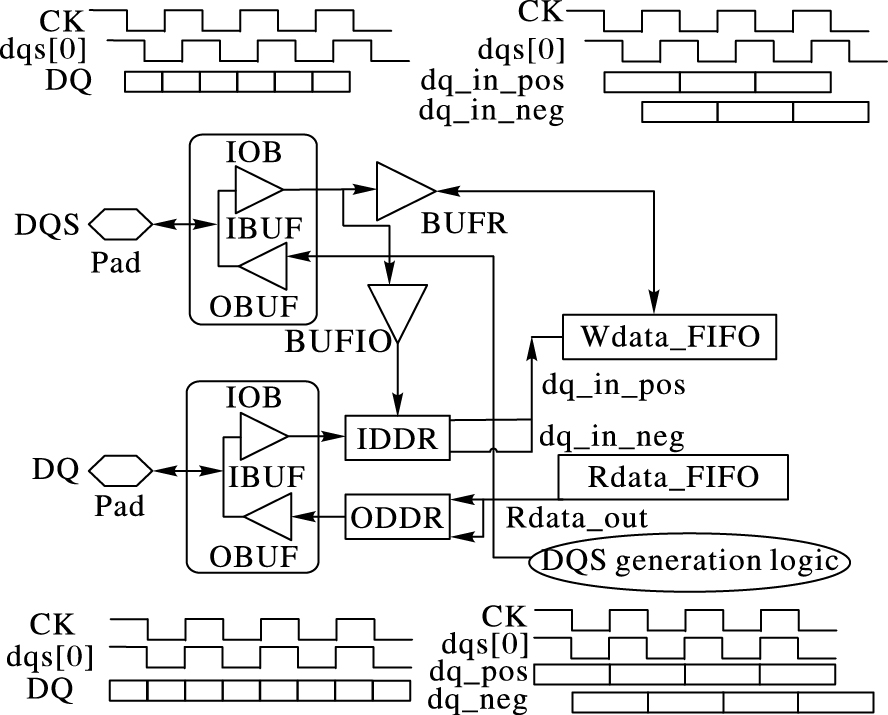

本文针对时钟资源的管理如图 6所示,采用三种不同的FPGA时钟资源分别驱动内部控制逻辑、数据采样逻辑和跨时钟域同步逻辑。其中,工作时钟CK/CK#走FPGA全局时钟网络,通过Xilinx时钟原语IBUGDS+BUFG具体实现, 驱动解析控制逻辑,以使解析逻辑可以在任意位置布局布线;而源同步时钟DQS使用FPGA的区域时钟资源,一方面通过I/O逻辑时钟缓冲BUFIO驱动数据采样逻辑,在接口位置完成采样功能,另一方面通过BUFR驱动数据的跨时钟域同步逻辑,完成写数据FIFO的跨时钟域同步,保证通过DQS采样到的数据能够在时钟CK下进行操作。

|

图 6 时钟资源管理 Figure 6 Clock resource management |

DDR3 SDRAM在时钟、地址、命令及控制信号上采用Fly-by拓扑结构[13],这些信号以菊花链的方式连接,串行地发送到各个内存芯片,以提高信号的完整性。由于数据信号DQ和选通信号DQS是以并行的方式发送到各个内存芯片颗粒的,因此造成了DQS信号与时钟信号CK之间的歪斜。在CPU正式进入读写访存状态之前,MC会自动对DDR3进行写平衡校准操作,调整相位使DQS和CK之间的偏斜变得最小。因此,本文设计的解析逻辑必须配合MC完成写平衡校准。

写平衡校准在时序上是一个反复而漫长的操作过程,其校准过程如图 7所示。DQS信号反复地采样时钟信号CK,并通过数据信号DQ将采样结果回送到内存控制器,内存控制器会根据采样结果对DQS信号作延时调整,以尽量使DQS与CK边沿对齐。

|

图 7 写平衡时钟信号采样 Figure 7 Write leveling clock signal sampling |

当解析逻辑检测到MC发出模式寄存器设置命令, 将MR1的A7地址位设置为1时,指示写平衡开始。解析逻辑不断采样CK、MC,不断调整DQS延时,反复调整直到MC确定DQS与CK之间的偏斜满足JEDEC规范的要求,才重新设置MR1,完成写平衡。本文通过仿真测试,统计出MC反复采样142次,DQS延时调整32次,最终完成时钟CK与DQS之间的偏斜调整,达到最小。

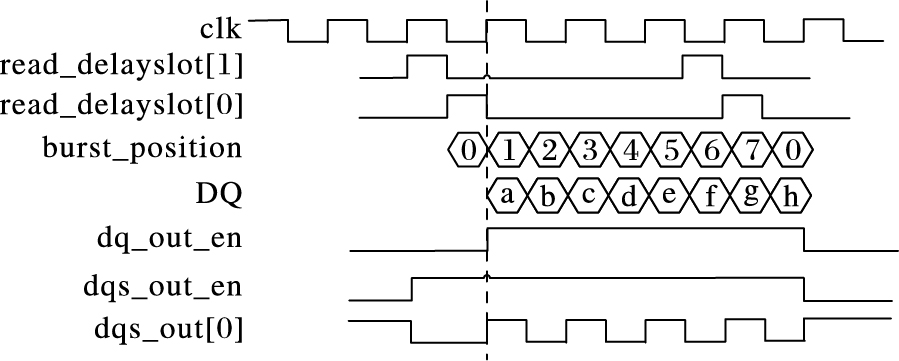

3.3 延迟槽为实现对延时的精确控制,在DDR3协议解析逻辑中加入延迟槽,即多组延迟计数逻辑。通常,DDR3存储器的性能可通过一系列的时序参数体现:tCL-tRCD-tRP-t RAS[14],例如DDR3-800的一组参数是6-6-6-15。这是一系列的时钟周期数,表示一个操作到另一个操作之间的延迟周期。比如从读命令发出,到数据读出送达接口之间延时为tCL,提早或稍晚读数据都会造成出错。

为保证满足DDR3接口的同步数据传输要求,本文中解析逻辑通过设置延迟槽来实现对操作时序上的精确控制。解析逻辑中共设置5个延迟槽:write_delayslot、read_delayslot、bank_delayslot、row_delayslot、col_delayslot,其中将write_delayslot和read_delayslot设置为15 b的一维向量,以记录读写命令发出后的延迟时间,将bank_delayslot、row_delayslot、col_delayslot设置成深度为15、宽度为相应地址宽度的二维向量,以保存读写命令发出时的地址信息Bank、Row、Col。

延迟槽中的向量数据在每个时钟沿右移一次,当零号向量位有效时表示对应命令进入数据操作阶段,开始采样数据或发送数据。延迟槽从侦测到读写命令时开始延时计数,对于读命令,命令发出后延时CL (CAS Latency) 个周期,将从存储器中取得的数据送达DDR3接口,开始将其拆分以数据流的形式输出;对于写命令,延时CWL (CAS Write Latency) 个周期数据到达内存总线,开始从接口提取有效数据并写入存储区。

如图 8所示为读延时控制,当read_delayslot[0]=1有效时,指示数据输出开始 (中间竖线位置),因此下一拍解析逻辑必须开始向DDR3接口发送数据。图中进行了8次数据触发,完成了一次BL=8的突发传输操作。与此同时, 使能各种控制信号并生成源同步信号,包括数据输出使能dq_out_en、突发传输位置burst_position、DQS输出使能dqs_out_en和DQS输出信号dqs_out等,精确控制其在时序上的有效时间。

|

图 8 延迟槽时序控制 Figure 8 Timing control by delayslot |

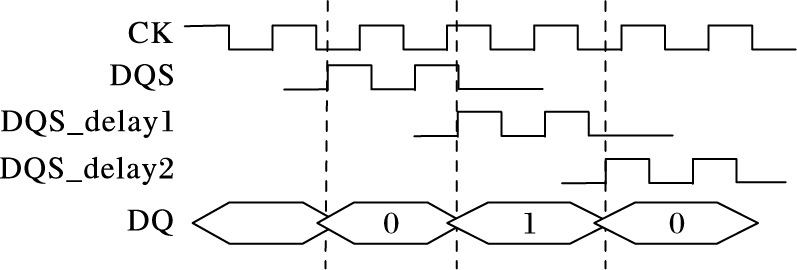

数据采样需要有精确的采样时钟。传统的共同时钟系统在频率提升到一定程度时,数据采样时序裕量不足,无法满足采样时序的要求,进而采用更加稳定有效的源同步时钟系统。在源同步时钟系统中,发送端将选通信号与数据信号同步发出,在接收端通过选通信号控制数据读取,选通信号即为源同步时钟信号。由于两个信号从发送端到接收端的飞行时间完全一致,从而保证了数据采样的准确性。

本文中选通信号DQS是数据信号DQ的源同步时钟信号,解析逻辑针对DQS和DQ的处理如图 9所示。在读写操作过程中,二者同步输入输出,确保数据采样的准确性:1) 图 9上方信号时序所示,在进行写操作时,选通信号DQS和数据信号DQ由内存控制器发送到解析逻辑,其中DQS与时钟CK中心对齐 (center-aligned),二者相位偏差90°,而数据信号DQ则直接与时钟CK边沿对齐 (eged-aligned)。解析逻辑使用DQS信号对DQ信号采样,采样位置在DQ有效周期的中心处,以此获得最大的采样时间裕度;2) 图 9下方所示,在进行读操作时,DQS和DQ由解析逻辑发送到内存控制器,并且二者均与时钟CK边沿对齐,在时钟CK的边沿触发下同时向DDR3接口发送,以保证在MC端数据采样的准确性。

|

图 9 DQS与DQ的I/O处理 Figure 9 I/O processing of DQS and DQ |

本文实验中对于输入数据信号使用IDDR原语,将它转换成两路单边沿触发的信号,在采样时钟DQS的上升沿处,一次性采样取得周期内的两拨数据 (如图 9右上角所示)。单边沿触发采样时间更长,以保证在FPGA内部数据采样的稳定性,提高设计的综合和实现效果。在读操作过程中,对于输出数据信号,数据在时钟上升沿一次性从FIFO中取得144 b数据,分成两路72 b数据 (如图 9右下角所示),用ODDR聚合成数据流输出,同时DQS生成逻辑会产生同步DQS信号数据往接口输出。

4 实验结果与分析实验采用Xilinx ISE软件生成的MIG核作为DDR3控制器,向DIMM口发送访存信号,并通过MIG核的用户接口,在用户逻辑中设计测试激励,模拟CPU向内存控制器发送访存命令。采用的DDR3类型为DDR3-800,理论峰值带宽为6.4 GB/s,采用的DDR3接口类型为适用于服务器内存插槽RDIMM口,接口数据位宽为72 b (64 b有效数据+8 b ECC校验)。DDR3协议解析逻辑采用Micron的MT18JSF51272PZ-1G4内存芯片的参数,工作频率为400 MHz,采用BL8突发方式进行数据传输。

实验分为正确性验证和读写性能测试两个部分:正确性验证检测协议解析逻辑在时序上的正确性;读写性能测试分为单次读写数据测试、连续读写数据测试和混合读写数据测试,分别验证解析逻辑的正确性和测试解析逻辑的有效性能。

4.1 正确性验证协议解析逻辑配合内存控制器完成初始化和校准过程,然后进入读写数据状态,并保证初始化和校准的正确性和读写数据的正确性,只有完成整个流程才能确认解析逻辑工作正常。

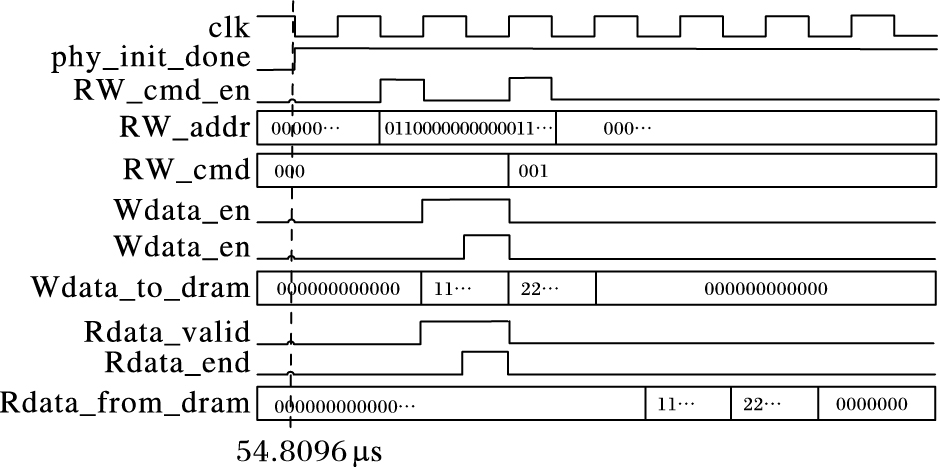

实验严格按照JEDEC标准的时序要求进行设计,完成了解析逻辑与控制器之间进行初始化及数据校准的交互过程,并在MIG核的用户接口 (UI) 端生成的读写激励,通过仿真显示,解析逻辑能够正确地配合内存控制器完成数据的写入和读出,如图 10所示。

|

图 10 写后读正确性验证 Figure 10 Correctness verification of reading after writing |

UI端的phy_init_done电平信号拉高表示初始化及校准操作成功,从图 10中可以看出,在仿真的54.8 μs处 (虚线指示),初始化及校准工作完成。之后,验证写、读数据的正确性,在UI端将数据256′h11111111111111AA11111111111111BB1111111111111CC11111111111111DD和256′h22222222222222AA22222222222222BB22222222222222CC22222222222222DD共512 b数据通过Wdata_to_dram信号写入解析逻辑,写入地址为30′b011jsjyy-37-5-12231110111100000000。写完成后发送读命令,从同一地址将数据读出,通过Rdata_from_dram将数据读回,图中仿真波形显示,读回的数据与写入的数据完全一致,从而验证了解析逻辑在配合内存控制器完成初始化及校准工作的正确性。

4.2 数据读写性能测试1) 单次读写性能测试。

为测试解析逻辑所能实现的性能,本文首先进行了单次读写数据测试。通过在MIG核的用户端采用Non-back-to-back模式 (非连续地址操作模式),产生多次独立的写数据和读数据激励,测试DDR3接口带宽的利用率。

实验中共进行200次独立的数据读写测试,其中100次写数据测试和100次读数据测试,分别测试在同Bank同行、同Bank不同行、不同Bank地址上的读写性能。其中在同Bank同行地址上读写性能最好,分别达到4.31 GB/s和3.2 GB/s,DDR3-800接口带宽利用率达到67.3%和50.0%。同Bank不同行地址上的读写性能最差,仅有1.2 GB/s和1.31 GB/s。这种差别主要源于内存控制器的访存机制。对于同一Bank行上数据的连续操作,内存控制器不进行行切换,即不需要对前一访问行进行预充电,从而大幅减少了两次读/写操作的时间间隙,提高了带宽的利用率。对于不同Bank地址上的读/写测试,由于两次操作的Bank位置不同,因此对前一个Bank预充电的同时可激活另一个Bank,从而平滑地过渡到对两个Bank的访存,因此读写性能比同Bank同行模式稍差,但比不同Bank不同行模式要好一倍左右,读/写性能分别达到3.69 GB/s和2.75 GB/s,DDR3-800接口带宽利用率为57.65%和42.96%。在同Bank不同行上进行数据访问,每次从一行中完成读/写后,需要对该Bank行进行预充电,此时这个Bank都不能做其他的操作,因此,同Bank内不同行之间切换时间开销比较大,读/写性能也最差。

2) 连续读写性能测试。

内存控制器的访存位置连续,读写性能会获得较大的提升。本文实验中进行了连续地址读写测试,在MIG核的用户接口端使用Back-to-back模式,向同Bank同行的连续列地址上发送访存命令,测试读写数据的性能。

在同Bank同行连续列地址上写数据速率达到4.41 GB/s,带宽利用率为68.90%,而读数据速率达到4.98 GB/s,接口带宽利用率为77.81%。两种连续读写模式都比单次读写模式中的同Bank同行模式下的性能高出15%~30%。连续地址访存过程中,由于地址连续,只需在第一个数据读/写时进行地址访问,后续地址在原有地址上加上固定偏移即可,因此减少了列地址寻址时间,提高了访存性能。

3) 混合读写性能测试。

现实情形中,CPU向内存控制器发出的读写命令很可能是混合在一起的,既有可能读后写,也有可能写后读,读写数据之间可能还存在相关。本文实验模拟CPU产生混合读写激励,在激励中读写操作不断切换,测试随机数据读写性能。实验结果如表 2所示。

| 表 2 混合读写性能 Table 2 Mixed read and write performance |

实验中,连续的两个读写命令地址不相同,即连续操作的数据不存在相关性,由此观察时间开销。实验数据显示,混合读写的带宽利用率普遍较低,为DDR3接口峰值带宽的20%~45%,其中连续读写操作地址在同Bank同行时,读写性能相对较高,数据传输速率到达2.76 GB/s,而连续读写操作地址在同Bank不同行时性能最低,仅为1.47 GB/s。这是由于在进行读写操作切换时,同Bank不同行地址上的读写只能串行地操作,由此引入的时间开销比较大。

5 结语基于DDR3接口设计SSD在位置上更加靠近CPU,具有较短的访存路径,因此在性能上具有巨大的优势。本文在总结和分析了DDR3存储器工作原理的基础上,根据JEDEC规范的时序,设计了DDR3接口信号解析逻辑,完成了协议解析功能,保证了SSD与内存控制器交互的正确性。实验结果表明,解析逻辑能够正确地完成与内存控制器的交互,并取得较为理想的I/O性能,为后续实现DDR3接口的SSD原型系统奠定了良好的基础。本文MIG配置命令顺序执行,在一定程度上限制了数据访问性能,在本文基础上,可对MIG配置成命令乱序执行,以优化设计;并且在本文基础上,后续可采用DDR3-1600或者DDR4接口,充分发挥内存接口性能的优势,提升SSD的I/O访问带宽。

| [1] | MICHAEL K, MILLER K W. Big data:new opportunities and new challenges[J]. Computer, 2013, 46(6): 22-24. doi: 10.1109/MC.2013.196 |

| [2] | OUYANG J, LIN S, JIANG S, et al. SDF:Software-defined flash for Web-scale internet storage systems[J]. ACM SIGPLAN Notices, 2014, 49(4): 471-484. |

| [3] | IHS homepage[EB/OL].[2016-05-20]. https://www.ihs.com/index.html. |

| [4] | BAEK S H, PARK K W. A fully persistent and consistent read/write cache using flash-based general SSDs for desktop workloads[J]. Information Systems, 2016, 58: 24-42. doi: 10.1016/j.is.2016.02.002 |

| [5] | LUO J, FAN L, CHEN Z, et al. A solid state drive architecture with memory card modules[J]. IEEE Transactions on Consumer Electronics, 2016, 62(1): 17-22. doi: 10.1109/TCE.2016.7448558 |

| [6] | GALBRAITH R E, CLEVELAND L D, YU J, et al. Highly automated hardware and firmware RAID SoC design optimized for memory class storage devices[C]//Proceedings of the 2013 International SoC Design Conference. Piscataway, NJ:IEEE, 2013:282-285. |

| [7] | StorageAcceleration[EB/OL].[2016-05-20]. http://www.storageacceleration.com. |

| [8] | OIKAWA S. Performance Impact of New Interface for Non-volatile Memory Storage[M]//Software Engineering Research, Management and Applications. Berlin:Springer, 2015:1-13. |

| [9] | 黄万伟. Xilinx FPGA应用进阶[M]. 北京: 电子工业出版社, 2014 : 21 -29. ( HUANG W W. Advanced Xilinx FPGA Applications[M]. Beijing: Publishing House of Electronics Industry, 2014 : 21 -29. ) |

| [10] | BALAJI T, PALANISAMY Z V. Memory design considerations for DDR-3 SDRAM[J]. Asian Journal of Information Technology, 2007, 6(6): 720-725. |

| [11] | SPECIFICATION D D R S. Revision of JESD79-3[S/OL].[2016-10-20].http://www.jedec.org/. |

| [12] | LEE T, KIM D, PARK H, et al. FPGA-based prototyping systems for emerging memory technologies[C]//Proceedings of the 201425nd IEEE International Symposium on Rapid System Prototyping. Piscataway, NJ:IEEE, 2014:115-120. |

| [13] | CHEN C K, GUO W D, YU C H, et al. Signal integrity analysis of DDR3 high-speed memory module[C]//Proceedings of the 2008 Electrical Design of Advanced Packaging and Systems Symposium. Piscataway, NJ:IEEE, 2008:101-104. |

| [14] | LIN C S, TSAI Y C. System and method for processing booting failure of system:U.S. Patent 8296556[P]. 2012-10-23. |