随着信息化与大数据时代的来临,人们对于实时视频数据的采集与处理的需求越来越多元化,采集的视频数据从单一低分辨率朝向多路高分辨率发展,随之而来的问题是需传输处理的数据规模呈倍数增长,这对数据的传输处理平台的性能提出了更高的要求。嵌入式芯片,如FPGA(Field-Programmable Gate Array)、DSP(Digital Signal Processing)等的应用让嵌入式硬件平台的处理能力大幅度提升,但处理系统的性能瓶颈主要位于PC端与硬件板卡之间的数据传输效率上,因此跨平台传输总线的选择至关重要。

PCI Express(PCIe)是第三代高性能I/O(Input/Output)总线,在总线结构上进行了根本的变革,其变化主要体现在两个方面:一是由并行总线变为串行总线,二是采用了点到点的互连。它具有速度快,两端设备独享带宽,扩展灵活等诸多优点[1]。PCIe作为目前使用最频繁的高速总线,广泛用于PC端与外部设备的之间的通信,如何利用PCIe总线对大规模数据进行高效传输已成为研究热点[2-4]。

由于直接存储访问(Direct Memory Access, DMA)可以降低传输对系统CPU资源的占用率,显著提高系统运行效率, 可以达到更高的数据传输速率,而被大多数系统采用。文献[5-6]中DMA传输所需的地址和数据大小等信息均由PC端通过PIO(Programmed I/O)方式写入PCIe空间映射的状态寄存器BAR(Base Address Register)中,FPGA只能被动地等待PC端的发起DMA操作;同时由于现有的平台可支持的PIO读写带宽仅为2~4MB/s[7],DMA传输带宽为PCIe理论带宽的50%,不能最大限度地利用PCIe带宽资源,无法满足本系统的数据传输带宽需求。文献[8]中在FPGA中设置了地址表,驱动程序将初始化时PC端分配的地址空间写入该地址表内,这解决了由PIO读写带宽低而造成的DMA带宽不理想的问题;但这种方式对PC端存储的访问灵活性低,因为地址表在初始化时被更新,DMA工作时只能按照既定的顺序访问存储器空间,同时当大量的地址需存储时,地址表额外占用了更多的FPGA的存储资源。为了满足本项目的传输带宽需求并解决以上问题,本文在FPGA自带的PCIe硬核的基础上设计了一种DMA传输控制器,利用FPGA端设置的命令缓冲区,采用FPGA主控的DMA传输模式,解决了PIO写延迟对DMA传输的限制问题,并提出了一种动态拼接的DMA调度方法,对DMA传输请求进行动态调控,进一步减少了软硬件交互次数。通过实验表明,本设计实现了PC端与处理板卡之间的多路数据高效传输,并且可为类似的应用提供参考。

1 PCI Express 1.1 PCIe接口PCIe是一种分层的体系结构,由下至上分别为物理层(Physical Layer, PHY)、数据链路层(Data Link Layer, DL)以及事务层(Transaction Layer, TL)[9]。在硬件板卡端,目前许多FPGA芯片内部均提供了可选的PCI-E协议实现方案,其自带的Xilinx PCIe LogiCORE IP核实现了物理层及数据链路层协议,并对上层提供了事务层接口[10],用户利用该接口即可实现对PCIE设备的控制及访问,开发者只需完成事务层的设计即可,这样简化了开发流程并具有优良的可移植性。

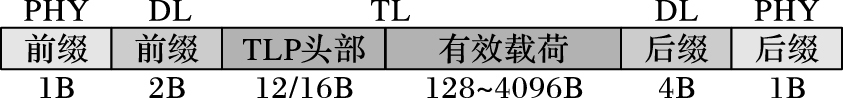

1.2 PCIe数据包组织结构PCIe总线通过数据包形式来实现信息的传递。 PCIe协议的事务可分为存储器事务、I/O事务、配置事务以及消息事务几个类型。TLP(Transaction Layer Packet)的包头被用于区分这些的事务,与此同时TLP数据包的包头也决定了当前TLP的路由信息等一系列信息。一个完整的PCIe数据包结构如图 1所示[11]。用户每次发送的数据都必须封装在这样的数据包格式内,但其中只有TLP头与有效数据载荷是用户层添加的,其余结构由PCIe物理层以及数据链路层额外添加到TLP上。

|

图 1 PCIe总线数据包结构 Figure 1 PCIe bus data packet structure |

PCIe Gen1每条链路单方向传输理论带宽为2.5Gb/s,PCIe Gen2将该速率提高了一倍,每一条链路的单方向理论带宽为5Gb/s[12]。由于PCIe Gen1和PCIe Gen2均使用了8b/10b的编码(80%),且由图 1可知,PCIe协议数据包含有额外的开销,所以PCIe总线带宽的理论最大值T(单位为Gb/s)的计算公式为式(1) :

| $T = {P \over {P + O}} \times N \times Gen \times 2\;$ | (1) |

其中:P为单个TLP最大有效载荷,O为TLP包头额外开支,N为链路总数,Gen为1或2,代表PCIe Gen1或PCIe Gen2。

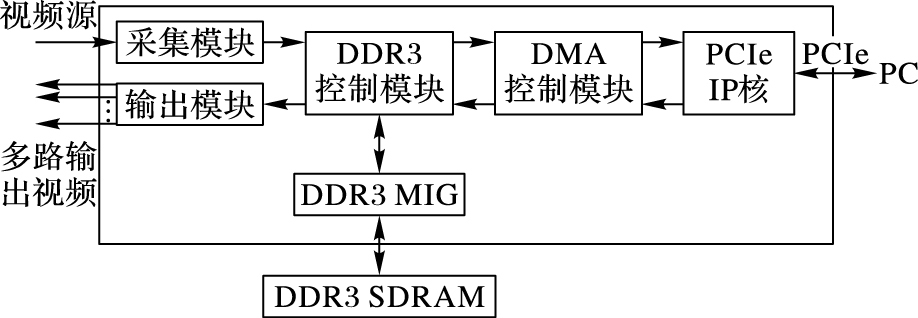

2 系统设计 2.1 系统结构及主要功能本系统有两个功能。一是FPGA将采集到的原始视频数据存储到DDR3 SDRAM中,用户请求数据后,FPGA通过PCIe总线将数据传输到PC端;二是PC端将经程序处理后的多路视频数据通过PCIE总线下传至FPGA端,FPGA读取这些数据并存储到DDR3。 FPGA与PC端的数据传输由DMA控制模块来调控。本项目中设计的多路视频采集处理系统的数据传输过程具有以下特点:1) PCIe下传参数时数据量大,板卡与PC端交互频繁;2) PCIe上传参数时数据量小,实时性要求高;3) 为防止数据溢出,FPGA端需要较大的数据缓冲区来存储PC端下传的多路视频数据。

针对这些特点,完成系统主要模块设计,系统结构如图 2所示。本系统主要模块包括PCIe IP核,DDR3 MIG模块、DMA控制器模块、DDR3读写控制模块以及视频采集输出模块。其中,PCIe IP核以及DDR3 MIG模块可以通过Xilinx CORE Generator工具按需求配置生成。下文将会具体介绍DMA控制模块的结构及DMA传输方法。

|

图 2 多路视频传输系统结构 Figure 2 Multi-channel video transmission system structure |

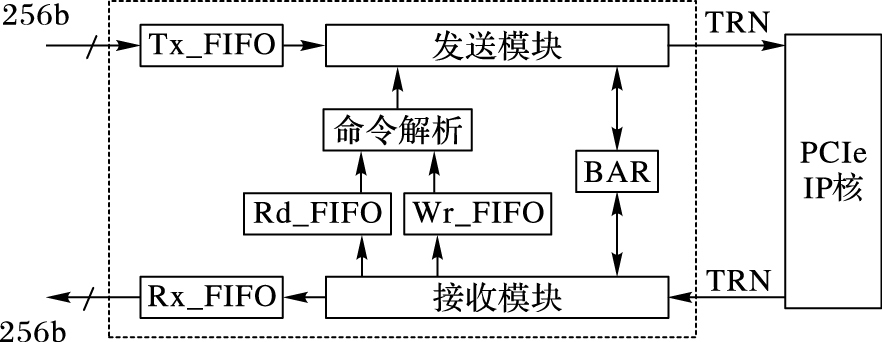

DMA控制模块包含发送模块、接收模块、BAR、读命令存储FIFO(Rd_FIFO)、写命令存储FIFO(Wr_FIFO)和命令解析模块,如图 3所示。

|

图 3 DMA控制模块结构 Figure 3 DMA control module structure |

两个数据宽度为256b的异步FIFO实现了DMA控制模块与DDR3读写模块的连接,解决了跨时钟域的问题。DMA控制/状态寄存器被映射到PCIe的地址空间中,也可和其他用户逻辑连接,用于控制DMA传输。

发送模块用于组织和传输转发事务、非转发事务和完成事务的数据包。发送模块可以产生存储器写请求包(Memory Write Request, MWr)、读请求包(Memory Read Request, MRd)和带数据的完成包(Completion with data, Cpld),产生的数据包发送到事务层接口(Transaction interface, TRN)。

接收模块支持完成事务、存储器读事务和存储器写事务。接收模块从TRN接口中接收事务包,并根据事务的种类,作出相应的操作。如接收到PC端的Cpld TLP时,接收模块将其中的数据段解析校验后存入RX_FIFO,等待存入DDR3;当接收到PC端的数据传输命令时,根据命令标志位将其放在对应的命令存储FIFO中。

命令存储FIFO将PC端发送的DMA读写命令顺序存储,命令解析模块从FIFO中读取命令,解析命令后通过发送模块组织相应TLP向PC端发起DMA存储器访问请求。

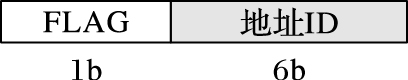

PC端发送的DMA请求命令格式为如图 4所示,其中FLAG标志位占1b,用于判断该命令为DMA读请求或DMA写请求,地址块对应id号占6b,PC端最多可设置64个缓冲区。

|

图 4 DMA请求命令格式示意图 Figure 4 Schematic diagram of DMA request command format |

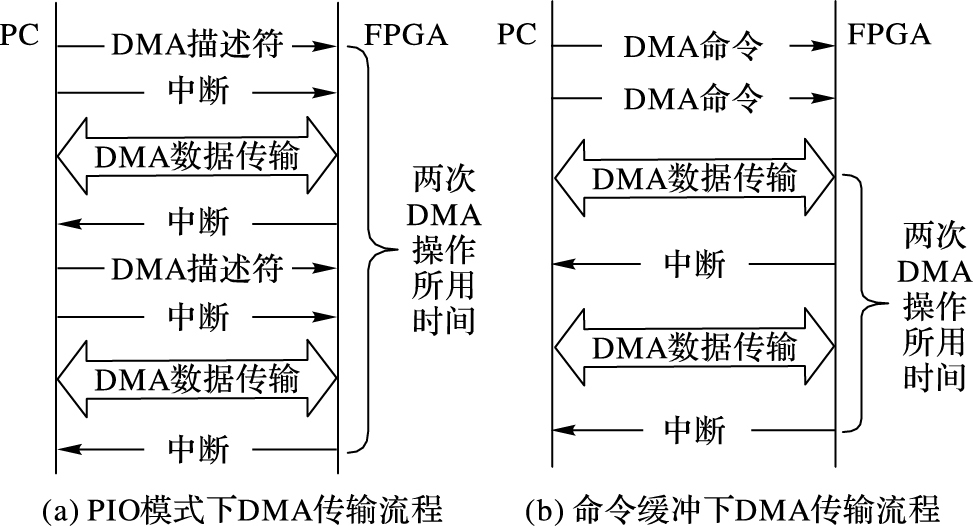

采用PIO方式的DMA读写操作流程一般为:PC端准备好数据后,向FPGA端BAR空间对应的位置写入代表触发DMA中断的数值,同时将DMA操作所需的起始地址及传输大小等信息一并填入BAR对应位置,FPGA检测到中断后开始进行DMA读操作。由于对同一地址同时读写会导致数据发生错乱,PC端会将对应的内存地址锁死,不再更新这些地址的数据。这种方法实际上是由PC端来发起DMA操作,DMA读写带宽受到了PC端工作主频的影响,特别是面对PC端需要向FPGA传输大量数据的应用场景时,实际环境所测得的带宽远远低于PCIe的理论带宽。本文在FPGA端增加了命令存储区,使得FPGA可根据自身需求动态地请求PC端的数据。两种方式对应的PC与FPGA的交互过程如图 5。图 5(a)为PIO方式PC与FPGA DMA传输示意图,图 5(b)为采用命令缓冲机制后的DMA传输示意图。可见采用命令缓冲机制后,DMA搬运同样大小数据的传输时间减少,传输涉及的中断处理操作减少,DMA带宽由此提升。

|

图 5 DMA传输流程对比 Figure 5 DMA transfer process comparison |

采用命令缓冲机制后,FPGA从PC端利用DMA读取数据的具体过程如下:

1) PC端在驱动程序中申请一段数据缓冲区,缓冲区被分为N部分,分别对应N路数据,编号为0~N-1,地址块大小为4KB,第i号地址块的起始地址add_start_i的计算公式为式(2) ,即基地址add_read_base加上偏移:

| $add\_start\_i = add\_read\_base + i \times 4000$ | (2) |

2) PC端向ID为i的地址块填充好数据后,向FPGA发送携带该地址块的ID号的命令,表示该部分数据可供读取。

3) FPGA端接收模块收到DMA传输命令后,通过判断flag标志位的值将命令存储到读命令存储FIFO或写命令存储FIFO中。

4) FPGA端的数据量低于预先设定值后,命令解析模块从读命令存储FIFO中取出一个命令,读取该命令ID号,通过式(2) 计算出PC端对应的起始地址,由发送模块组织PCIe存储器读请求TLP发送到PC端,请求命令对应的地址数据。PC端收到读请求后,会自动将相应地址内的数据打包成Cpld发回给FPGA,这个过程并不需要PC端CPU的参与。

5) FPGA端的接收模块接收到Cpld TLP,解析后将其中携带的数据按顺序存入到RX_FIFO中,等待存入DDR3。当整个DMA读操作完成后,FPGA向主机发送一个中断。

6) PC接收到中断后,根据中断信息判断哪块地址数据被读取,并将对应数据缓冲区更新。回到步骤2) 。

2.2.3 DMA写操作DMA写操作与DMA读操作类似,若FPGA内的DMA存储器写操作需要等待PC端操作BAR空间内寄存器才能发起,不仅占用了CPU的时钟周期,而且每一次启动DMA时FPGA都需要等待CPU,影响了DMA的带宽吞吐量。

1) PC端在驱动程序中申请一段内存,缓冲区被分为N部分,编号为0~N-1,地址块大小为4KB,第i号地址块的起始地址add_start_i计算公式为式(3) ,即基地址add_write_base加上偏移,PC端需要读取第i块地址的数据时,将其ID值打包发送给FPGA:

| $add\_start\_i = add\_write\_base + i \times 4000$ | (3) |

2) FPGA端接收模块收到DMA传输命令后,通过判断flag标志位的值将命令存储到读命令存储FIFO或写命令存储FIFO中。

3) FPGA端采集到的数据量大于预先设定值后,命令解析模块从写命令存储FIFO中取出一个命令,通过式(3) 计算出CPU端对应的缓冲区起始地址,由发送模块组织PCIe存储器写请求TLP发送到PC端。PC端接收到写存储器请求,解析TLP提取出数据放至对应地址内。

4) FPGA完成DMA写操作后,向主机发送一个中断,表示该块数据已更新。PC端可根据中断信息,取用对应缓冲区的数据。

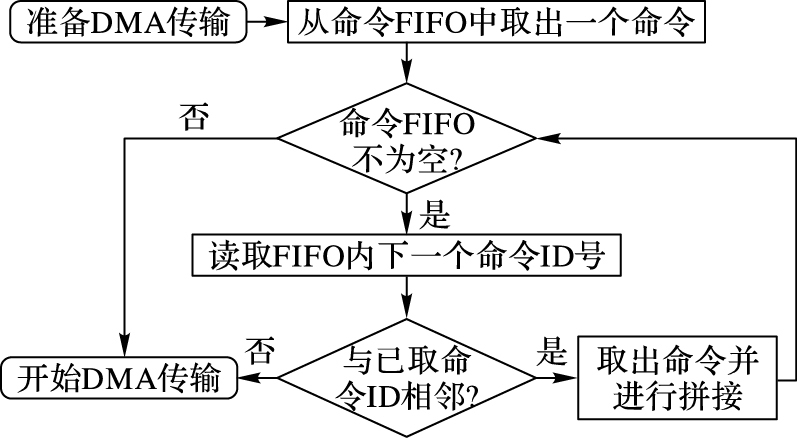

2.2.4 基于动态拼接的DMA调度方法为了进一步提升DMA传输带宽,一种基于动态拼接策略的DMA调度方法被用于DMA传输控制。以进行DMA存储器读操作为例,当FPGA准备进行DMA传输时,命令解析模块从命令存储FIFO中取出一个命令后,若FIFO仍存有命令,命令解析模块将继续判断下一个命令的ID号,若该命令ID号与之前命令的ID号可相邻,即意味着两次DMA操作PC端的地址相连,则命令解析模块取出该命令并将两个命令拼接成一个DMA传输请求,当FIFO仍不为空时,这种DMA拼接将继续,直到下一个命令的ID号与已有的ID号不连续或FIFO为空为止。这种将对相邻地址的DMA读操作动态的拼接成一次DMA操作的调度方法,减少了两次DMA配置之间的时间,进一步提升了PCIe DMA传输效率。DMA调度流程如图 6所示。

|

图 6 DMA调度流程 Figure 6 DMA scheduling process |

当DMA不进行动态拼接时,一次DMA传输DMA完成操作后通知PC端的数据更新的地址ID号。多次DMA传输需多次中断;但若DMA采用了动态拼接策略,多个命令传输完成后,仅需一次中断通知PC端DMA操作更新的地址区间。利用动态拼接策略,减少了PC端需处理的DMA传输中断数量,降低了CPU中断处理所造成的延迟。

3 实验结果 3.1 实验环境本设计采用实验室自主研发的多路视频输出板作为实验平台,并结合对应的驱动程和应用程序进行测试。该平台支持GEN1×8模式的PCIe链路,并且使用Xilinx公司的Kintex-7 XC7K325T作为主控芯片,采用Xilinx ISE14.7作为开发工具,利用Verilog语言完成FPGA程序设计。DDR3 MIG配置读写控制时钟400MHz,数据位宽256b。PCIe core配置为GEN1×8模式。板卡通过PCIe接口连接主机,CPU为Intel i7处理核,工作主频为2.8GHz,操作系统为Windows 7 pro。

按照本文系统模块设计,自顶向下完成FPGA各模块代码的编写与优化,通过ISE综合、映射与布局布线后,整个设计占用Register资源6713个,占用LUT资源6782个,占用Block Ram/FIFO资源12个,可以看出本系统对于FPGA资源占用率较少,有利于后续工作的展开。

| 表 1 FPGA资源占用表 Table 1 FPGA resource occupancy table |

视频传输过程由本文中设计的DMA控制器控制,实验分别测试DMA读与DMA写带宽。PC端以2μs的间隔向FPGA发送N个数据传输命令,TLP的有效载荷设置为512B。应用程序端使用函数QueryPerformanceCounter()计数传输一定大小的DMA数据块需要的计算机周期数,并利用函数QueryPerformanceFrequency()读取CPU时钟周期,DMA传输带宽计算公式如下,其中P为TLP有效载荷,n为所用CPU周期数,tc 为CPU时钟周期。

| $T = {{N \times P} \over {n \times {t_c}}}$ | (4) |

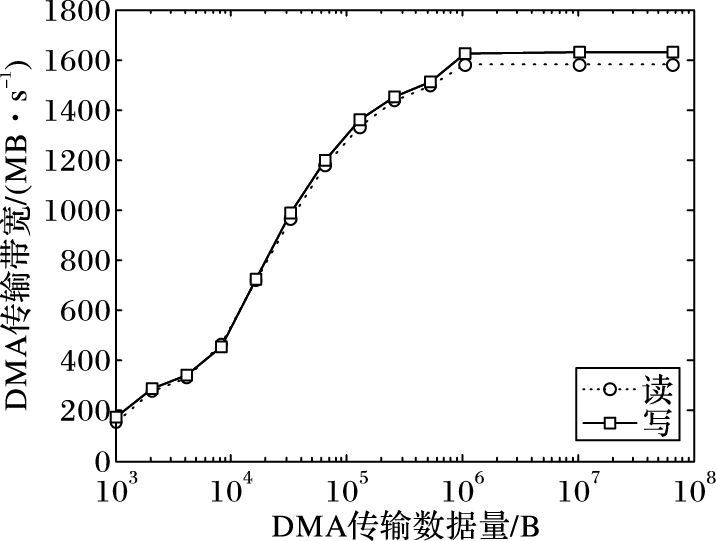

DMA读写带宽与DMA传输不同大小的数据量的关系如图 7所示。通过实验结果可以得知,随着DMA传输数据量的增大,DMA读写带宽均随之增加,当传输数据量从10KB增加到100KB时,带宽增长幅度最大,当传输数据量达到一定程度时,带宽增长缓慢。最高DMA读带宽为1582MB/s,最高DMA写带宽为1631MB/s,峰值带宽达到理论带宽值的85%。

|

图 7 DMA传输带宽变化曲线 Figure 7 DMA transmission bandwidth variation curve |

表 2为本文方法与其他文献方法在DMA读写带宽方面的比较。文献[4]和文献[13]中采用由PC端通过PIO更改DMA状态控制寄存器的模式进行DMA传输。文献[4]中采用PCIe GEN1×4通道接口板,DMA写速率为539MB/s,读速率为504MB/s。文献[13]中所用平台为GEN1×8 PCIe链路,DMA写速率最高为1311MB/s,DMA读速率最高为1002MB/s。将速率均换算为PCIe GEN1×8通道进行比较,本文DMA传输方式与PIO方式相比,DMA写速率平均可提升36%,DMA读速率平均可提升58%。

| 表 2 DMA传输带宽对比 Table 2 DMA transmission bandwidth comparison |

针对实际的多路视频数据的传输需求,本文提出了一种基于命令缓冲机制的DMA传输机制,采用FPGA主动控制的DMA传输模式,降低了PIO写延时对于DMA传输带宽的影响,同时提出了一种基于动态拼接的DMA调度方法,进一步提升了DMA传输带宽。实验结果表明,该系统DMA写最高速率可达1631MB/s,DMA读最高速率可达1582MB/s,达到了PCIe理论带宽值的85.4%;与利用PIO方式的DMA传输机制相比,本方法DMA读带宽提升58%,DMA写带宽提高36%。但目前为止,PC端每个ID号对应的数据存储区大小相等,只能传输大小固定的数据块,以后考虑在命令中增加新的字段来表示传输数据大小。

| [1] | PCI-Special Interest Group. PCI express 2.0 base specification revision 3.1a[EB/OL].[2016-02-07]. http://www.pcisig.com/specifications/pciexpress/base2/. |

| [2] | BITTNER R, RUF E. Direct GPU/FPGA communication via PCI express[J]. Cluster Computing, 2014, 17 (2) : 339-348. doi: 10.1007/s10586-013-0280-9 |

| [3] | CORREIA M, SOUSA J, COMBO A, et al. Implementation of IEEE-1588 timing and synchronization for ATCA control and data acquisition systems[J]. Fusion Engineering and Design, 2012, 87 (12) : 2178-2181. doi: 10.1016/j.fusengdes.2012.07.012 |

| [4] | DE LA CHEVALLERIE D, KORINTH J, KOCH A. ffLink:a lightweight high-performance open-source PCI express Gen3 interface for reconfigurable accelerators[J]. ACM SIGARCH Computer Architecture News, 2015, 43 (4) : 34-39. |

| [5] | 李木国, 黄影, 刘于之. 基于FPGA的PCIe总线接口的DMA传输设计[J]. 计算机测量与控制, 2013, 21 (1) : 233-235. ( LI M G, HUANG Y, LIU Y Z. Design of DMA transmission with PCIe bus interface based on FPGA[J]. Computer Measurement and Control, 2013, 21 (1) : 233-235. ) |

| [6] | 邹晨, 高云. 基于FPGA的PCIe总线DMA传输的设计与实现[J]. 电光与控制, 2015, 22 (7) : 84-88. ( ZOU C, GAO Y. Design and implementation of DMA transmission with PCIe bus based on FPGA[J]. Electronics Optics and Control, 2015, 22 (7) : 84-88. ) |

| [7] | BITTNER R. Speedy bus mastering PCI express[C]//Proceedings of the 201222nd International Conference on Field Programmable Logic and Applications. Piscataway, NJ:IEEE, 2012:523-526. |

| [8] | ROTA L, CASELLE M, CHILINGARYAN S, et al. A PCIe DMA architecture for multi-gigabyte per second data transmission[J]. IEEE Transactions on Nuclear Science, 2015, 62 (3) : 972-976. doi: 10.1109/TNS.2015.2426877 |

| [9] | THOMA Y, DASSATTI A, MOLLA D, et al. FPGA-GPU communicating through PCIe[J]. Microprocessors and Microsystems, 2015, 39 (7) : 565-575. doi: 10.1016/j.micpro.2015.02.005 |

| [10] | Xilinx. LogiCoreTM IP endpoint for PCI express V3.7 user guide[EB/OL].[2016-03-08]. http://www.xilinx.com. |

| [11] | GONG J, WANG T, CHEN J, et al. An efficient and flexible host-FPGA PCIe communication library[C]//Proceedings of the 201424th International Conference on Field Programmable Logic and Applications. Piscataway, NJ:IEEE, 2014:1-6. |

| [12] | KAVIANIPOUR H, MUSCHTER S, BOHM C. High performance FPGA-based DMA interface for PCIe[J]. IEEE Transactions on Nuclear Science, 2014, 61 (2) : 1-3. doi: 10.1109/TNS.2014.2315888 |

| [13] | 侯杭呈, 王忆文, 李辉. 一种基于PCI Express总线的DMA高速传输系统[J]. 微电子学, 2013, 43 (3) : 383-386. ( HOU H C, WANG Y W, LI H. A high-speed DMA transmission system based on PCI express bus[J]. Microelectronics, 2013, 43 (3) : 383-386. ) |